# Self-adaptation of Cyber Physical Systems: Flexible HW/SW computing

Eduardo de la Torre eduardo.delatorre@upm.es

Summer School on Cyber Physical Systems Alghero – 25/29 Septmber 2017

Universidad Politécnica de Madrid

#### A use case for motivation: the SPACE environment

## Why adaptation in space?

- Cost is becoming as determinant as radiation

- Resources are starting to be shared

- Same cameras used for navigation and scientific missions

- Algorithms change from one function to other ightarrow Reconfiguration needed

- Flash memories for space cannot be rewritten that often

- SRAM-based FPGAs with many design protections are being considered

- New business models are being projected

- Farms of satellites offering specific services (Power, communications)

- But, out of LEO, MEO or GEO, systems are fully alone

- Nobody knows what will be there

- Some missions are commanded to define Science on the spot

- Autonomy (Self-\*) is required

POLITÉCNICA

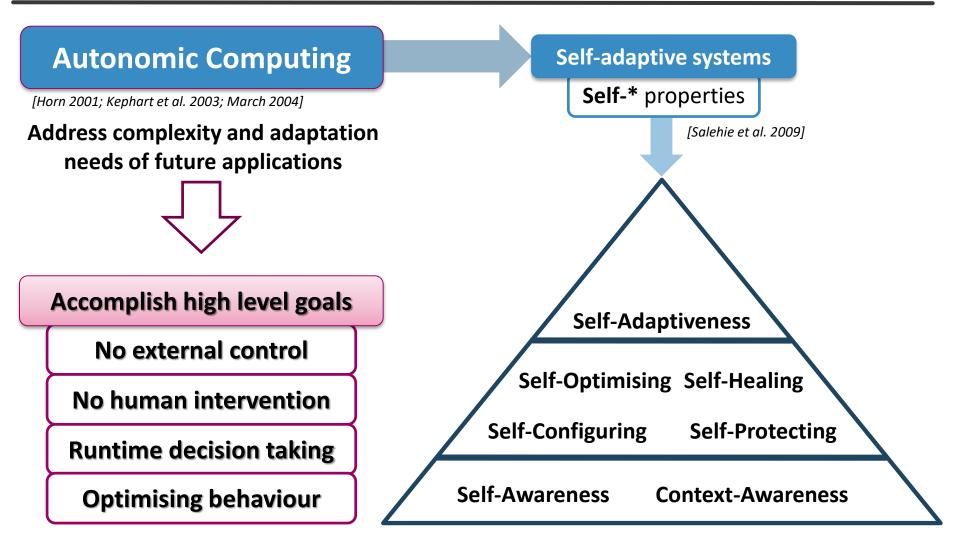

## **Autonomous System Adaptation**

### **Towards more robust and autonomous systems**

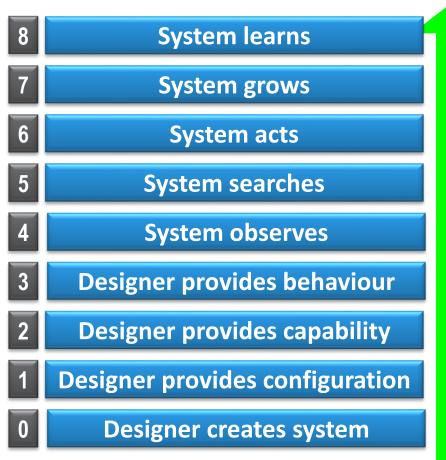

#### Levels of autonomy

Source: 'HW autonomy and space systems', Steiner & Athanas IEEE Trans on Automation Control, 2009

#### With reconf. devices

**Evolvable HW**

**Scalable HW systems**

Adaptability, self-healing

**Evolutionary algorithms**

**Power-aware systems**

**Offline genetic algorithms**

**Self-configuration**

**Remote configuration**

**Off-line design**

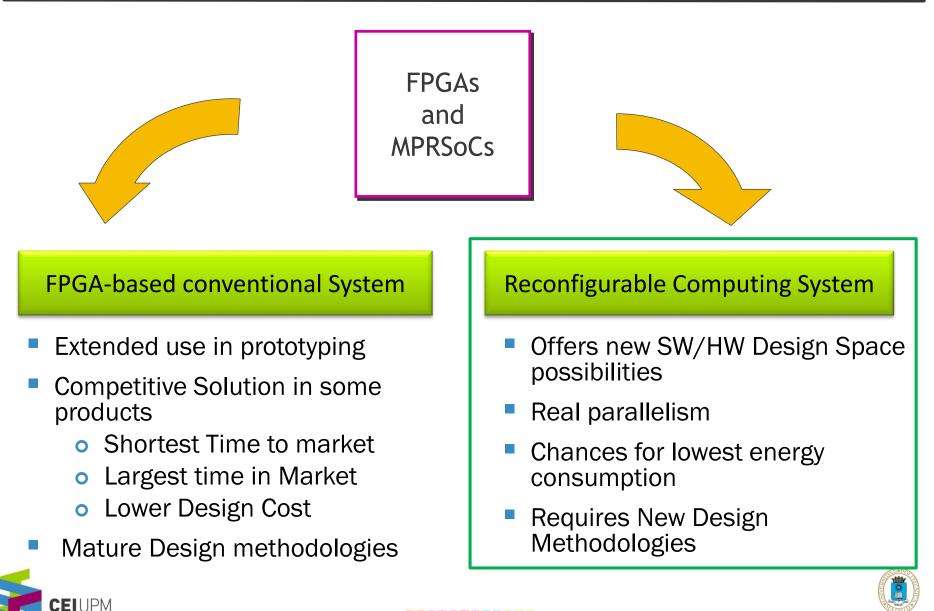

## Can reconfigurable computing help in this?

#### Time-multiplexing of tasks

- Complex systems in smaller devices

- The IKEA concept applied to circuits

#### Reduction of energy consumption

- Dark silicon is reduced (dark silicon occupies area, spends energy, and does nothing!)

- It allows to make more efficient circuits, since there is more place to do things better (quality, performance), or with less energy.

#### Autonomous and adaptive systems

- Adaptable Security & Communication Standards

- Bioinspired computing

- Dependability by design

Theoretically, reconfiguring an FPGA is as simple as changing a SW program:

# It's just writing in a memory !!

## **Reconfigurable systems on heterogeneous platforms**

# **THE ARTICO<sup>3</sup> ARCHITECTURE**

Summer School on CPS – Alghero Spetember 2017

## **ARTICo3: Motivation**

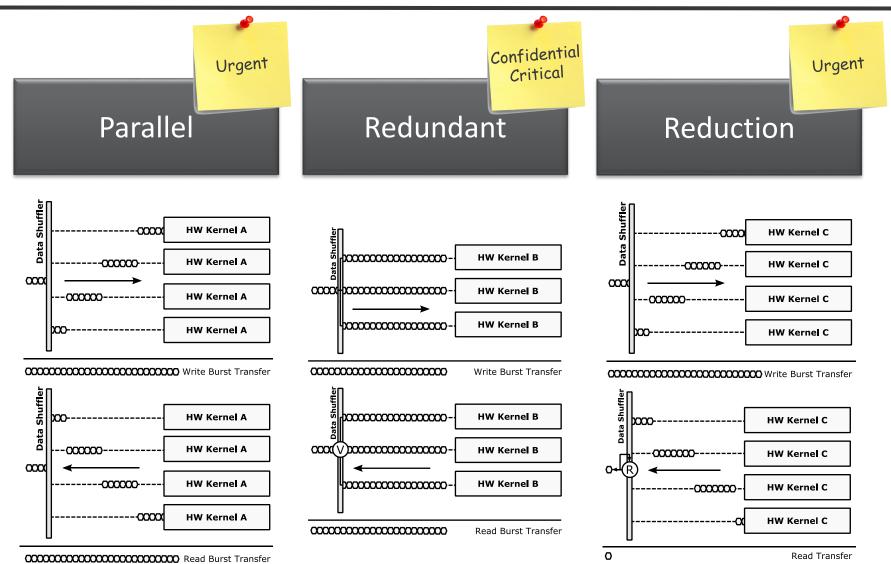

(hardware acceleration + module replication)

### How to transfer data efficiently

The memory side

The accelerators' side

Efficient transactions (coalesced accesses) are planned by the programmer, So they can be more efficient than caches.

In Artico3, accelerators don't claim for data, these are given in an organized manner by a scheduler

High Performance Embedded Computing Platforms

#### Architectures

#### Design Flows

### Runtime Environment

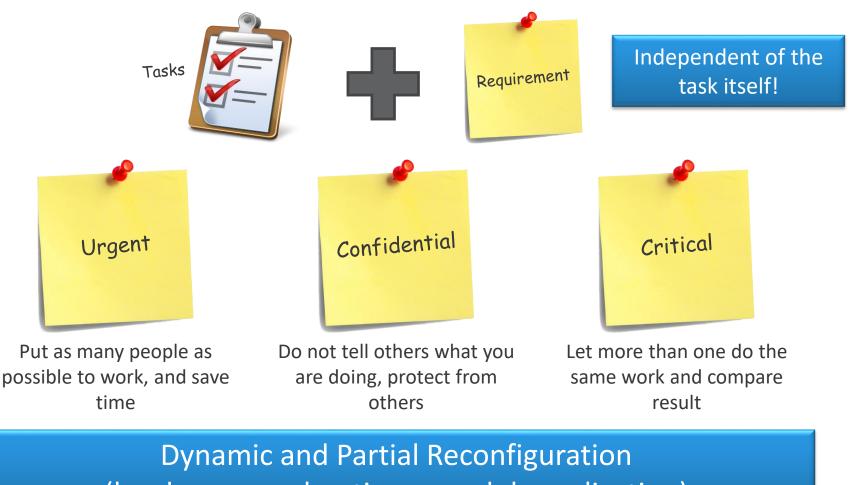

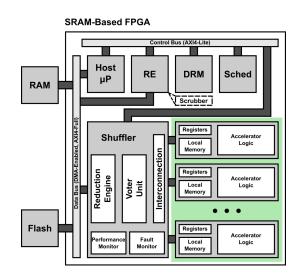

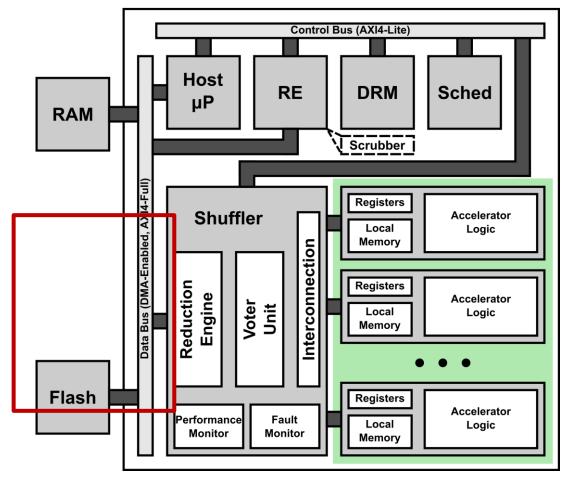

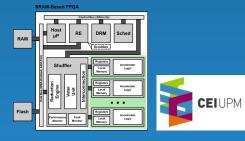

## **ARTICo3: Computing vs consumption vs fault tolerance**

SRAM-Based FPGA

Smart Gateway between AXI4 and Custom P2P Communication

Summer School on CPS – Alghero Spetember 2017

#### **Data Transaction Modes**

Summer School on CPS – Alghero Spetember 2017

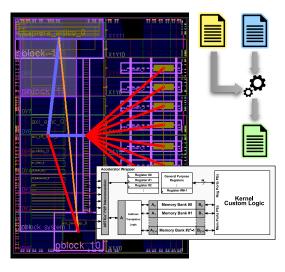

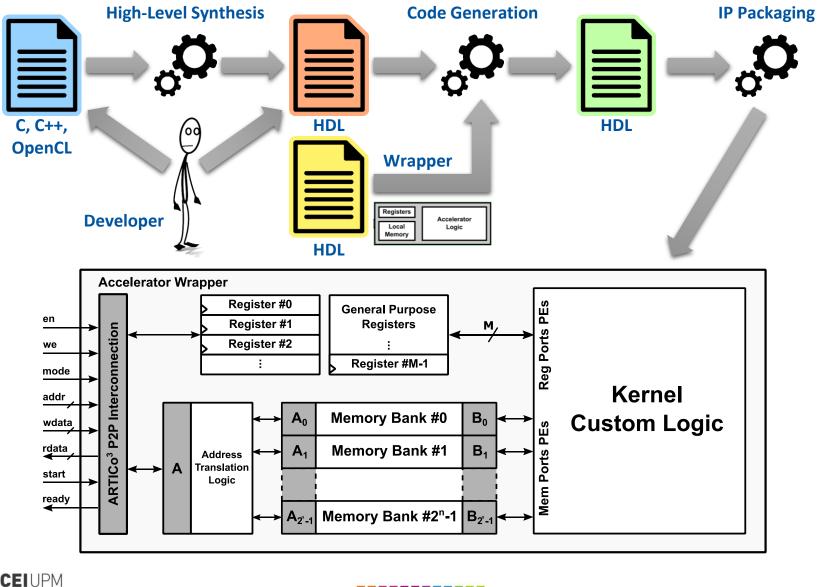

## **ARTICo3-Compliant Accelerator Design**

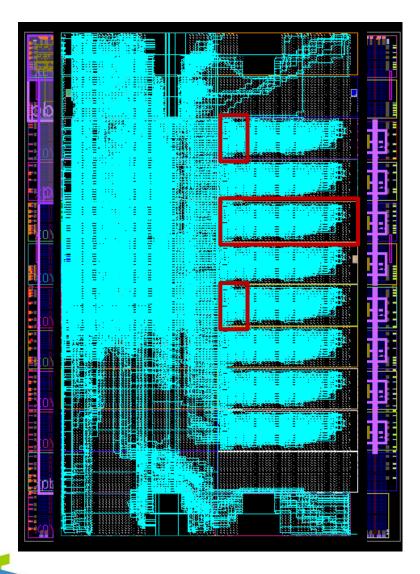

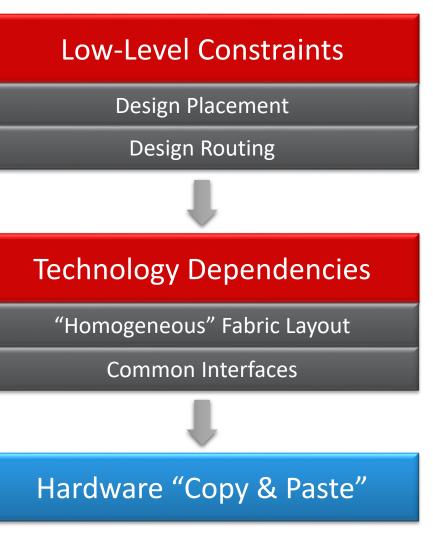

## **DPR-Compatible Floorplanning**

CEIUPM

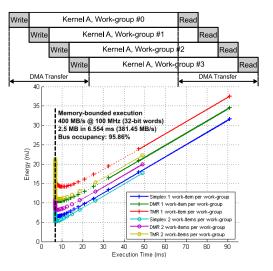

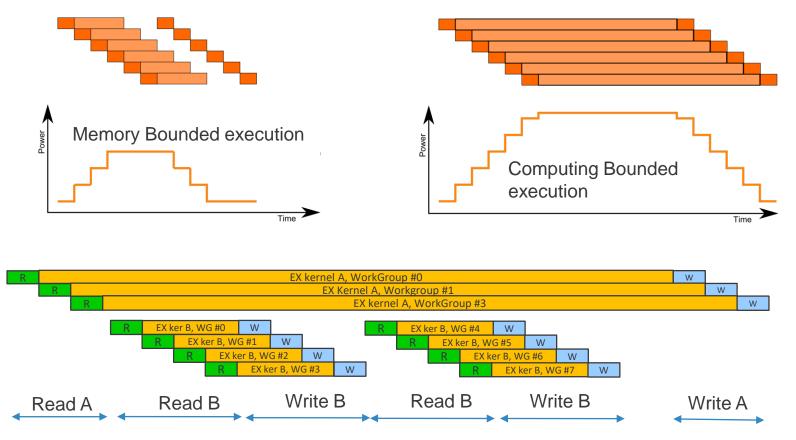

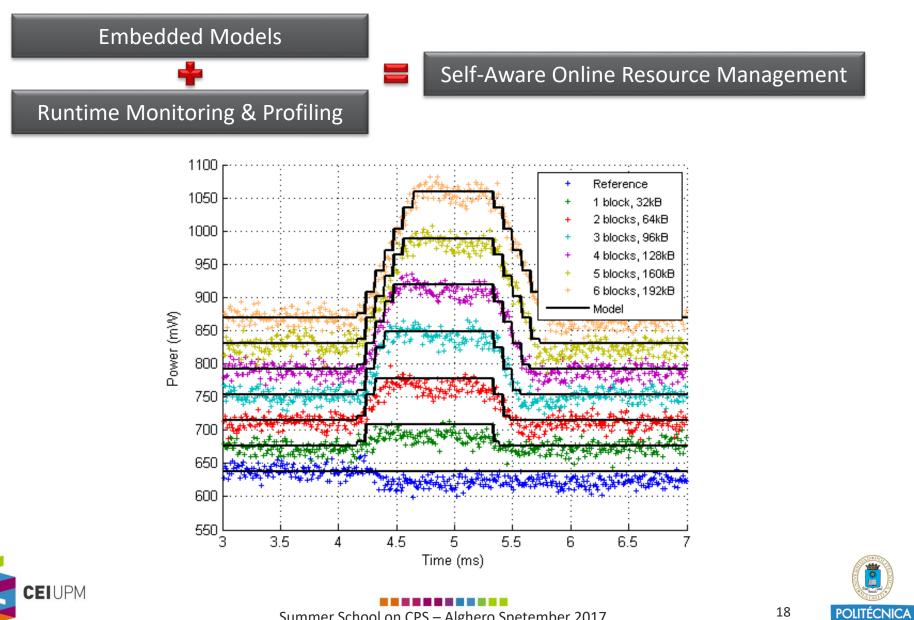

## **Execution and energy modelling**

EUPM

Example execution of two concurrent kernels. Kernel A is a long computing bounded execution run of 3 different Workgroups, while B uses memory access 'dead time' to execute two bunches of 4 Workgroups each for kernel B. Memory accesses optimised: only 6 transactions, máximum memory utilisation

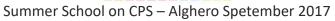

### **Dynamic Solution Space Exploration**

#### **Embedding the model for self-adaptation**

## What's next?

- ReconOS + ARTICo<sup>3</sup> integration

- Different programming models

- HW/SW multithreading (ReconOS)

- OpenCL-like coprocessing (ARTICo<sup>3</sup>)

- Common needs

CEIUPM

- Simultaneous multitasking support

- SoA DPR support

- Integration challenges

- Is it possible/feasible to merge both programming models?

- How can both frameworks benefit from multitasking capabilities (i.e. the reconfigurable fabric is used by several applications at the same time)?

- Does it make sense to provide last ReconOS version with DPR capabilities using ARTICo<sup>3</sup> as part of the underlying hardware infrastructure?

- Does it make sense to have an OpenCL-like coprocessing engine in ReconOS-based systems?

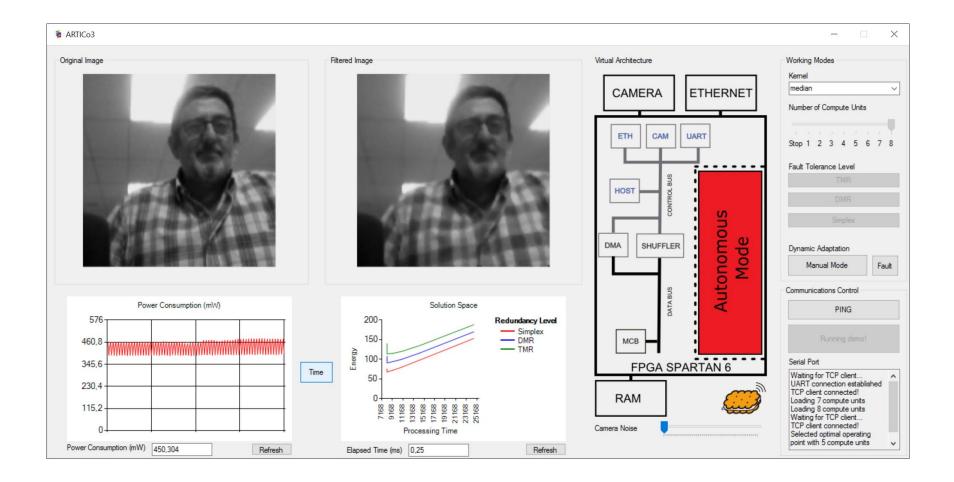

SRAM-Based FPGA

## Next: Hardening for extending the applicability

Design diversity:

3 reconfiguration types: external (JTAG, other), internal (PCAP & ICAP) 2 scrubbers, external and internal (slow and fast loops) HW & SW tasks, all relocatable → Heterogeneity to survive Graceful degradation

21

## **Further into HPC**

Intel and other chip makers are increasingly relying on accelerators to help improve the performance and energy efficiency of their processors and speed up the workloads that run on them. Nvidia and Advanced Micro Devices offer GPU accelerators. However, the company also is now using FPGAs, which can be reprogrammed through software after they've been manufactured. They're becoming more important for cloud and Web-scale environments, where workloads can change quickly. (Source: Jeffrey Burtenews, April 2016)

Achronix Introduces the Highest FPGA Memory Bandwidth, PCIe Acceleration Board for Data Center Applications (Source: Achronix, 2016 June 21<sup>st</sup>) (700,000 LUTs, 6 memory controllers 690 Gbps, PCIe v3x8, 4x 40G Ethernet, ...) ... and outstanding regularity!!! → Perfect for DPR

CEIUPM

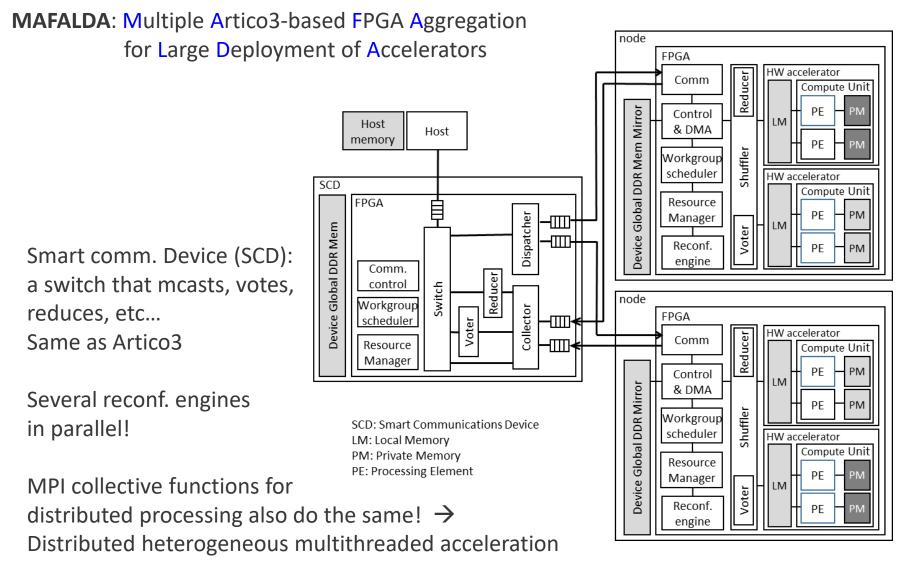

## A cluster of ARTICo<sup>3</sup> nodes: towards HPC

CEIUPM

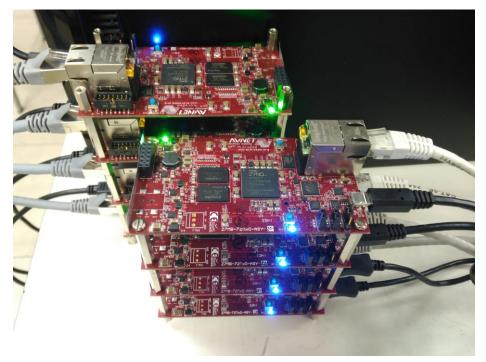

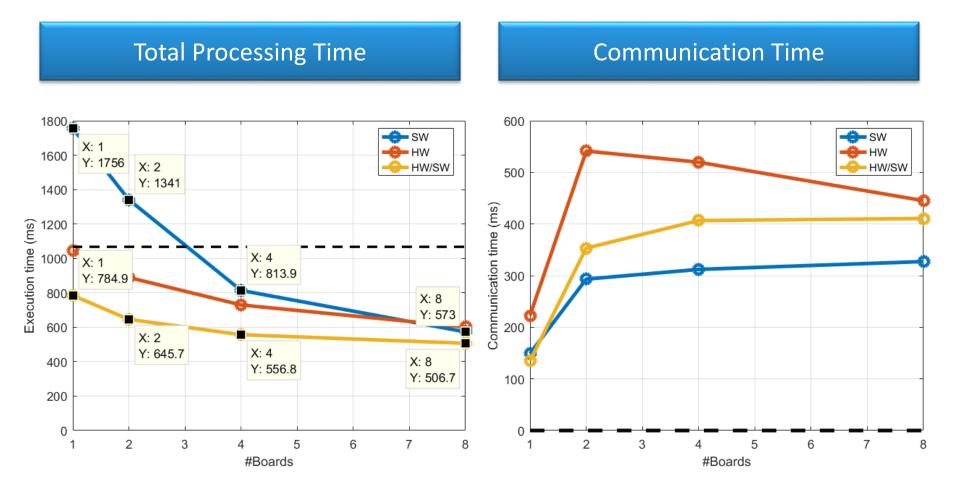

### **Multi-FPGA acceleration**

- Small FPGA-based computing cluster

- ARTICo<sup>3</sup> infrastructure per node

- Resilient MPI-based communication

- Work in progress

- HLS-based standalone accelerators, need to use ARTICo<sup>3</sup>-based ones

- MPI-based communications, need to use fault-tolerant alternatives

## **ARTICo3 Ecosystem**

#### REBECCA

• Basic Toolchain

CEIUPM

- Execution Modeling

- Multi-FPGA Extension

• Resilience in Smart Cities

#### Basic ARTICo<sup>3</sup> Platform

GOBIERNO DE ESPANA COMPUTITIVIDAL

H2020

Hardened for Space

- Safe Reconfiguration

- Scrubbing Techniques

Hyperspectral Image

**Autonomous Satellite**

• Predictability

Compression

Navigation

gn.

ThalesAlenia

•

@ \$\$ **# 7**

ENABLE S3

MINISTERIO DE ECONOMIA Y COMPETITIVIDAI

H2020

- Complete Toolset

- Full Adaptation

CERBER

- CPSs & CPSoSs

- Robotic Arm for Space Rover

ThalesA

Summer School on CPS – Alghero Spetember 2017

ULPGC

INSTITUTO TECNOLÓGICO

Space

- Adaptable platform

- Trading-off computing performance, energy utilization and fault tolerance

- Compatible with multithread execution models, so same code is OK for multicore, GPGPUs and FPGAs

- Scalable to HPC by congruent clustering (WIP)

- Some Self-\* features

- Self adaption triggered by lightweight embeddable execution models

- Self-awareness (conscious of energy and faults)

- Self-protecting by fault tolerance and task movement

- Going up towards more levels of autonomy

- Evolvable HW

EUPM

# **EVOLVABLE HW: TOWARDS SELF-\***

Summer School on CPS – Alghero Spetember 2017

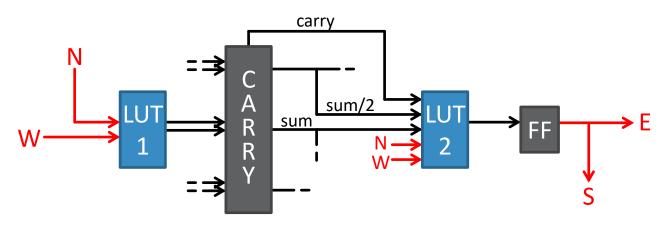

## **Computing Engine – Architecture**

Adaptable Computing Template

**Unknown Processing Behaviours**

**Runtime Reconfigurable**

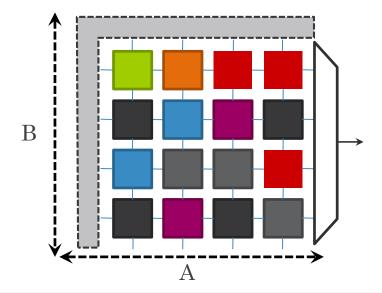

### **2D Systolic Array of Reconfigurable PEs**

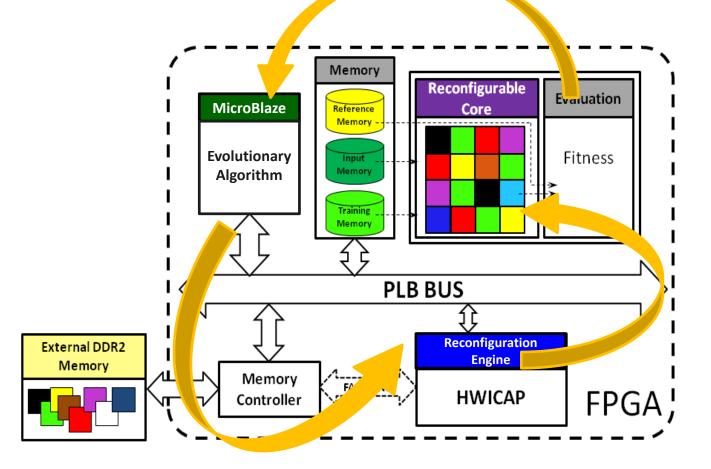

### The SoPC architecture

An Evolvable HW System based on a single processing array

CEIUPM

A. Otero, R. Salvador, J. Mora, E. de la Torre, T. Riesgo, L. Sekanina; "A fast Reconfigurable 2D HW core architecture on FPGAs for evolvable Self-Adaptive Systems", AHS 2011

Summer School on CPS – Alghero Spetember 2017

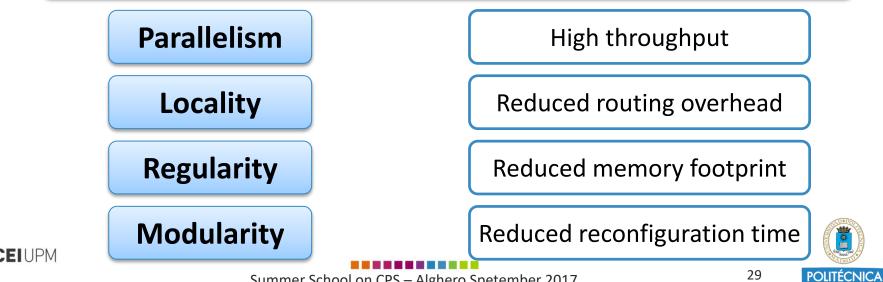

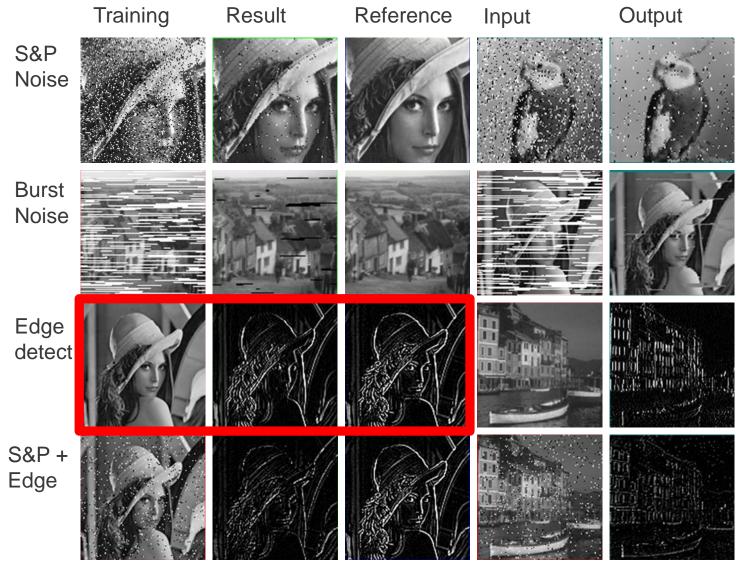

## System is adaptable and generalizable

## Scalability and evolution for increased fault tolerance

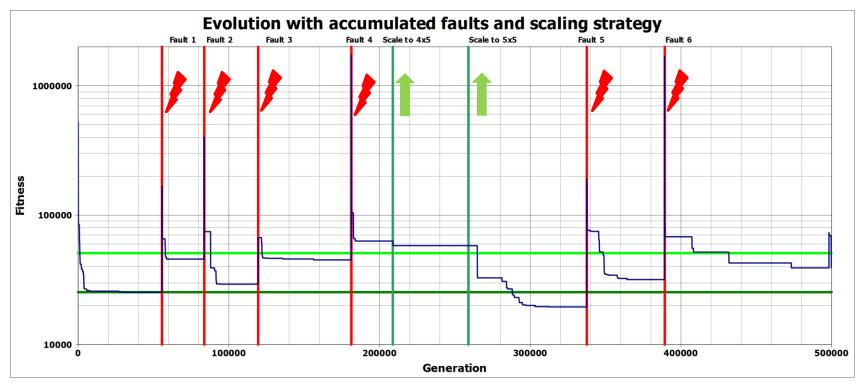

#### Improved fault tolerance provided by intrinsic evolution

Example of evolution with accumulated faults (threshold at 2x initial fitness)

A 4x4 recovers from 2 faults in average A 7x7 recovers from 12 faults in average

CEIUPM

Lifetime of the system extended 6 times

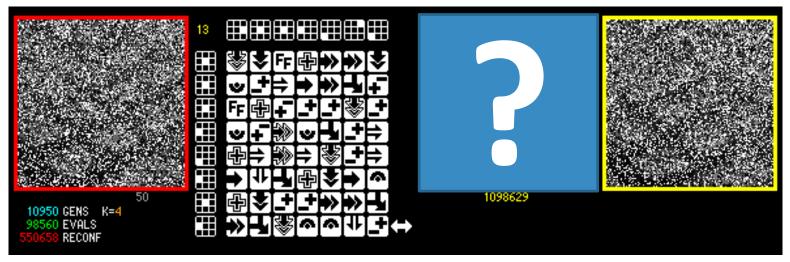

### **Results of a large array with very noisy reference**

With these two inputs .... We get this output

Noise-agnostic filter with autonomous self-healing physically-sclable scalable evolvable hardware

## **Processing array improved results**

LUT-based processing elements

• Small: 2 CLBs per PE

EUPM

- Fast: 450 MHz (450 Mpixels/sec) ← Because of locality!!

- Same functions / Possible new functions

- Only LUTs change → No routing restrictions

- Less to reconfigure: From 36 frames  $\rightarrow$  3 frames

- Evolution speed: 135000 evaluations/second (12 arrays on Virtex5)

- The world is becoming complex, and systems might need to be autonomous and adapt to changes w/o external intervention

- Full autonomy is obtained as a contribution of other interesting characteristics

- DPR, scalability, self-awareness, self-healing, ...

- Performance goes together with energy efficiency and dependability

- FPGAs and DPR are key players, in embedded and HPC

- There are many things left to be done → research oportunities

CEIUPM

#### Many things shown here today would not have been possible without the help of

- Teresa Riesgo, Jorge Portilla and Yago Torroja

- Ana Belén Jimeno, Yana Krasteva, Andrés Otero, Wei He, Rubén Salvador, Javier Mora, Juan Valverde, Filip Veljkovic, Alfonso Rodriguez, Leonardo Suriano

- Ángel Gallego, Blanca López, Julio Camarero, Santiago Muñoz, César Castañares, Carlos Giménez, Javi Vázquez, Gabriela Cabrera

- Miguel de las Heras, Ángel Morales, Manu Llinás, Alex Fernández, Miguel López, Pablo Sánchez, Carlos Pizarro, Verónica Díaz, Clara Casas, Miguel Baquero, Antonio Niño,, Javier Polop, Diego Lanza, Victor López, Ramón Conejo, Carlos Correa, Pablo Iglesias, David Gozalo, Alberto Ortiz

... thank you all for being a great (if not the best) team

- We also acknowledge the support from institutions

- European Union, Ministerio de Ec. y competitividad, Min. de Industria, Comunidad de Madrid

- Many thanks for the collaboration with past, present and future partners, and all those who shared the same illusions (and beers)

### ... "Become wáter, my friend"

"You must be shapeless, formless, like water. When you pour water in a bottle, it becomes the bottle. When you pour water in a teapot, it becomes the teapot. Water can drip and it can crash. Become like water my friend."

# Become like water, my hardware. Be shapeless, formless, like water