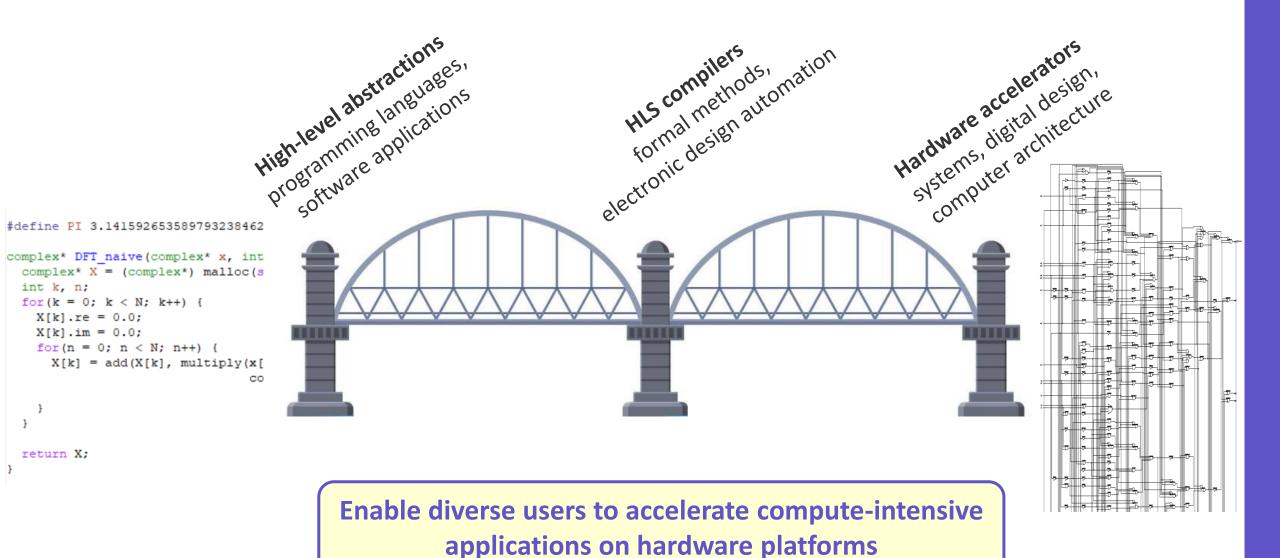

## From Software Programs to Digital Circuits

Lana Josipović

September 2023

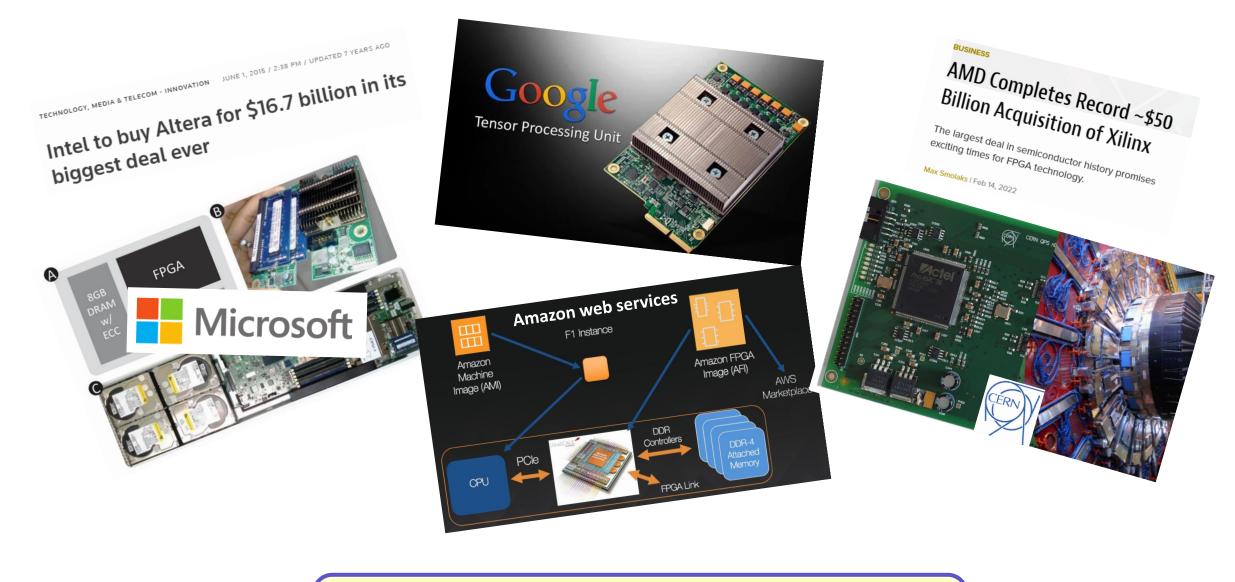

Hardware acceleration for high parallelism and energy efficiency

#### How to perform hardware design?

... circuit design is often considered a "black art", restricted to only those with years of training in electrical engineering...

[cacm.acm.org/magazines/2023/1/]

... chips take years to design, resulting in the need to speculate about how to optimize the next generation of chips...

[ai.googleblog.com/2020/04]

## **High-Level Synthesis: From Programs to Circuits**

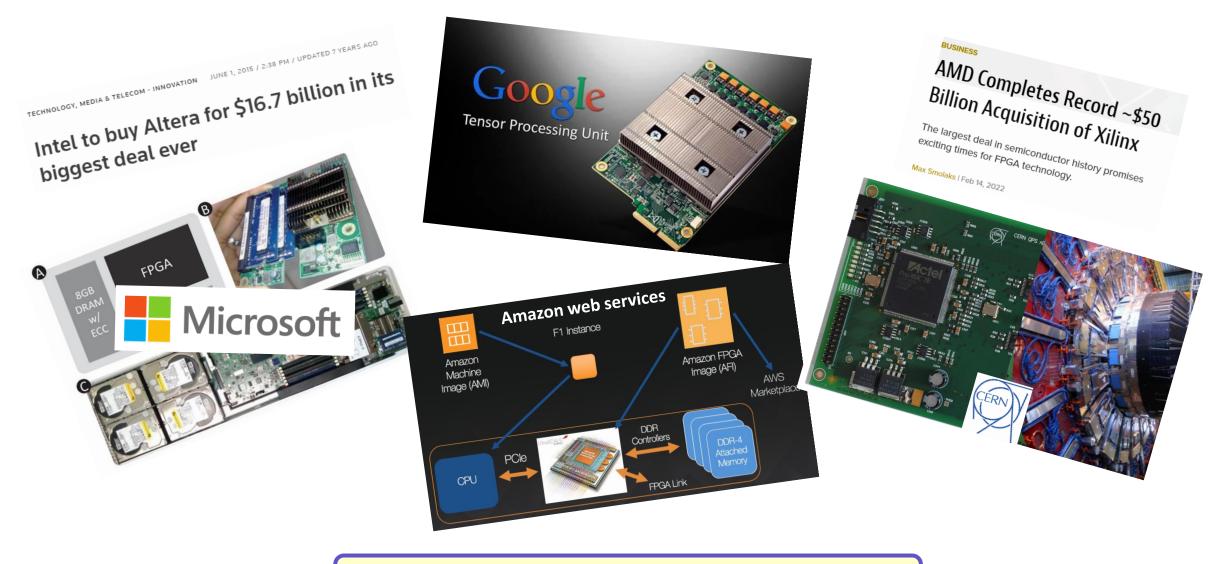

Raise the level of abstraction for hardware design beyond RTL level (VHDL, Verilog)

SW

HLS is still not meant for software programmers

SW

HLS is still not meant for software programmers

(a) Unoptimized HLS Program; Execution Time = 27,236 clock cycles

SW

HLS is still not meant for software programmers

```

void(int* mem) {

mem[512] = 0;

for(int i=0; i<512; i++)

mem[512] += mem[i];

}</pre>

```

(a) Unoptimized HLS Program; Execution Time = 27,236 clock cycles

```

1 // Width of MPort = 16 * sizeof(int)

#define ChunkSize (sizeof(MPort)/sizeof(int))

#define LoopCount (512/ChunkSize)

4 // Maximize data width from memory

5 void(MPort* mem) {

// Use a local buffer and burst access

MPort buff[LoopCount];

memcpy (buff, mem, LoopCount);

// Use a local variable for accumulation

int sum=0;

for(int i=1; i<LoopCount; i++) {</pre>

11

// Use additional directives where useful

// e.g. pipeline and unroll for parallel exec.

#pragma PIPELINE

14

for(int j=0; j<ChunkSize; j++) {</pre>

15

#pragma UNROLL

sum+=(int)(buff[i]>>j*sizeof(int)*8);}

mem[512]=sum;

```

(b) Optimized HLS Program; Execution Time = 302 clock cycles

George et al. FPL 2014.

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

```

for (i = 0; i < num_rows, i++) {

tmp = 0;

s = row[i]; e = row[i+1];

for (c = s; c < e; c++) {

cid = col[c];

tmp += val[c] * vec[cid];

}

out[i] = tmp;

}</pre>

```

Sparse-matrix dense-vector multiplication (SpMV)

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

```

for (i = 0; i < num_rows, i++) {

tmp = 0;

s = row[i]; e = row[i+1]; Variable memory latency

for (c = s; c < e; c++) {

cid = col[c];

tmp += val[c] * vec[cid];

}

out[i] = tmp;

}</pre>

```

Sparse-matrix dense-vector multiplication (SpMV)

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

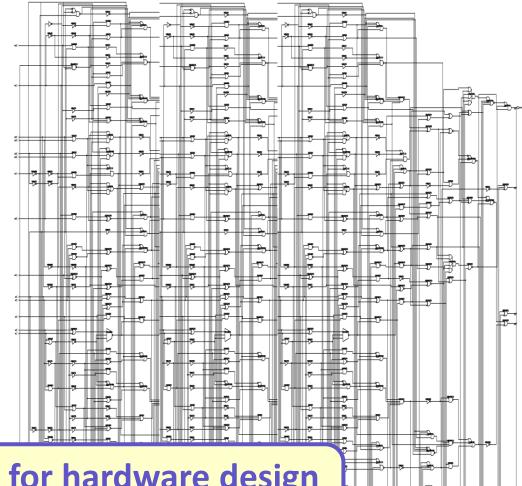

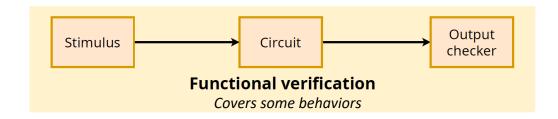

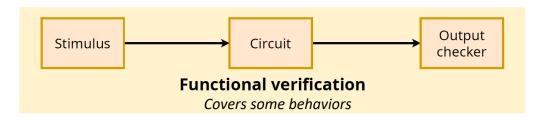

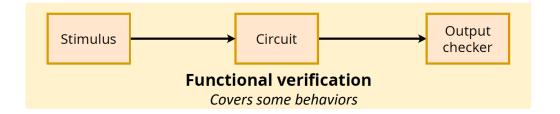

HLS circuits need hardware-level functional verification

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

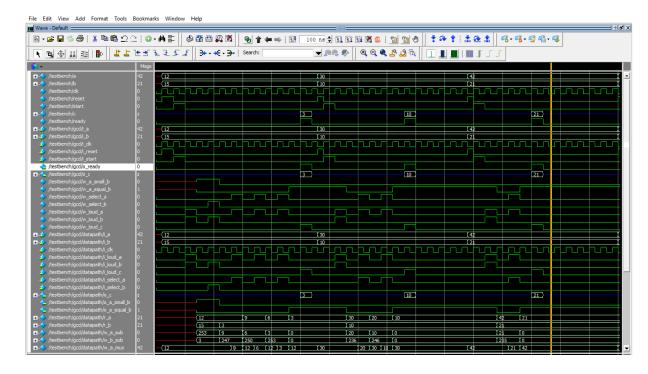

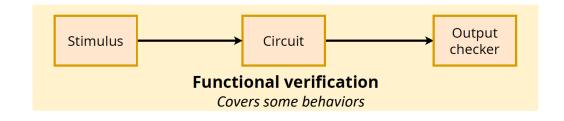

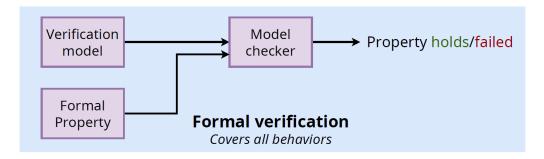

Functional verification of circuits using hardware simulation

→ inefficient, limited, non-exhaustive

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

Functional verification of circuits using hardware simulation

→ inefficient, limited, non-exhaustive

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

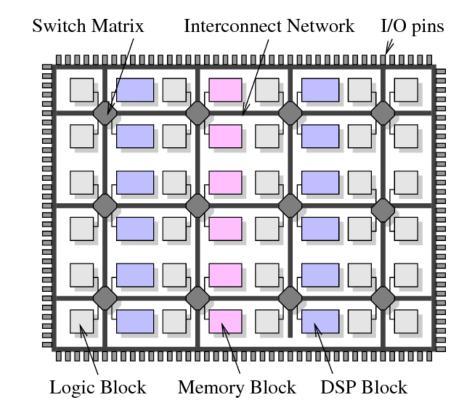

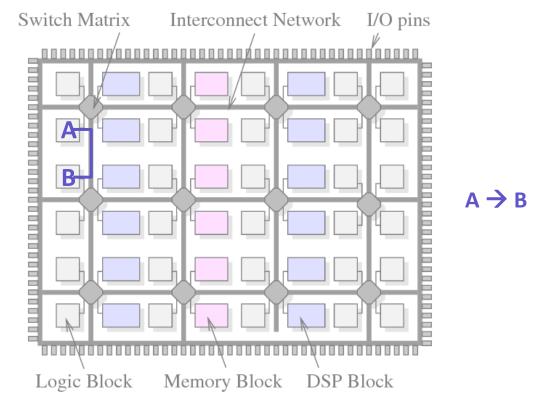

HLS circuits need hardware-level functional verification

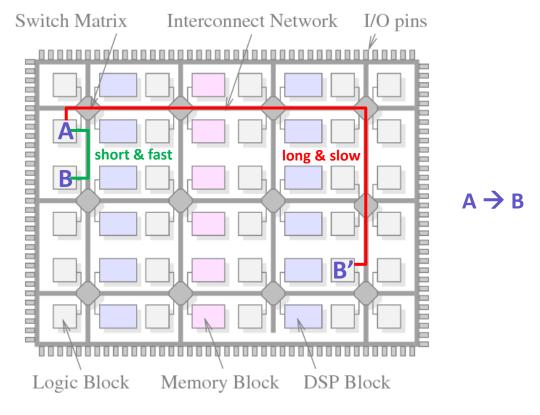

It is difficult for HLS to account for reconfigurable platform details

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

→ impact on circuit performance and power

Langhammer et al. ARITH 2015.

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

FPGA technology mapping, placement, and routing

→ impact on circuit performance and power

Langhammer et al. ARITH 2015.

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

FPGA technology mapping, placement, and routing

→ impact on circuit performance and power

Langhammer et al. ARITH 2015.

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

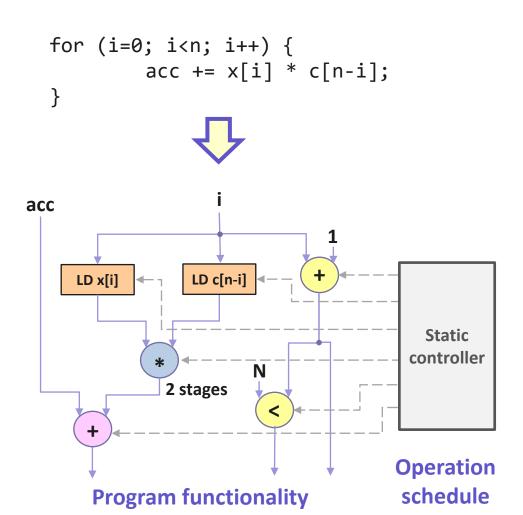

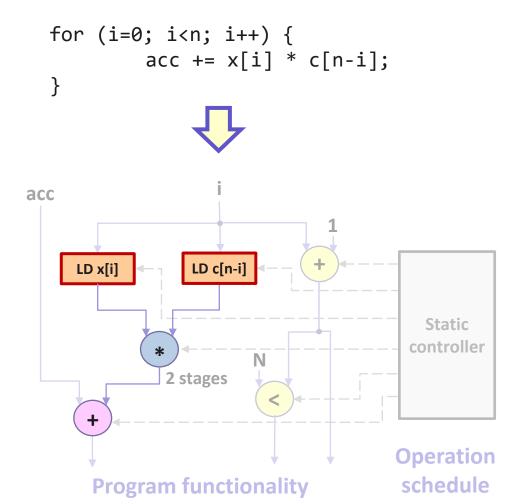

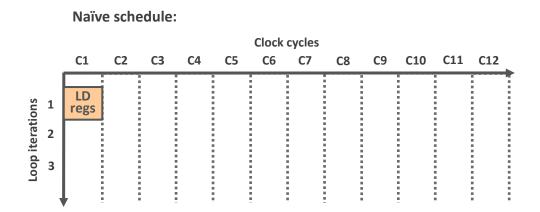

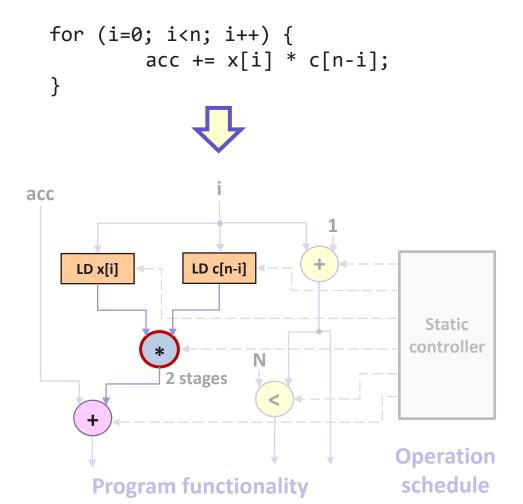

How to generate high-performance circuits from general-purpose software code?

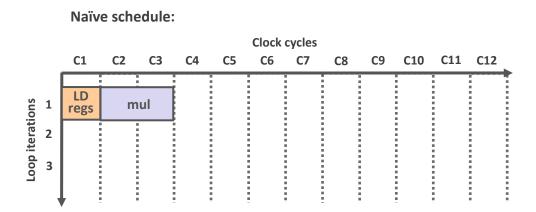

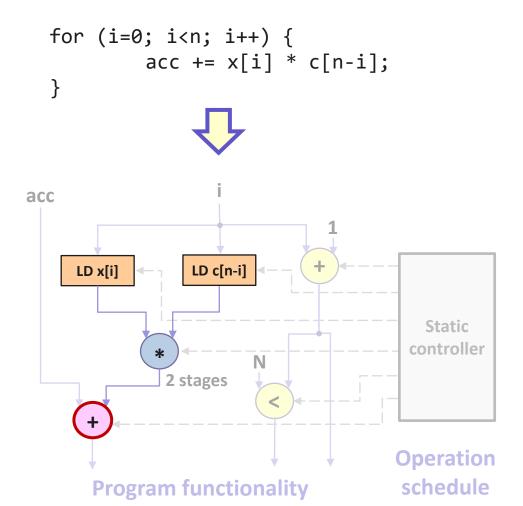

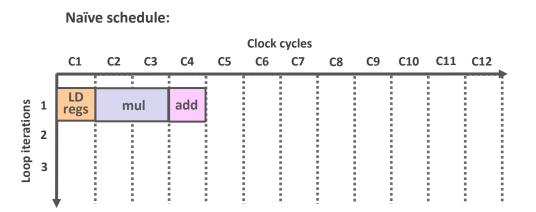

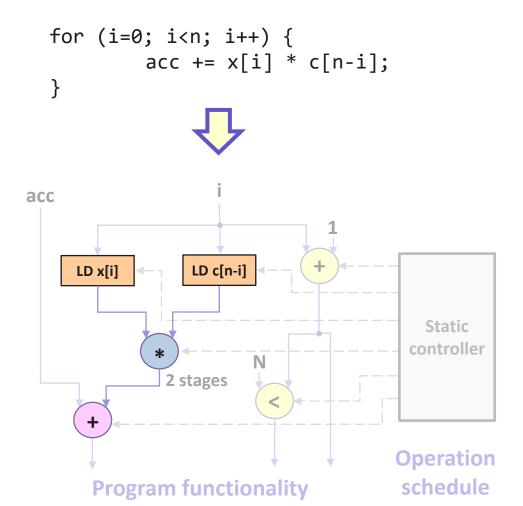

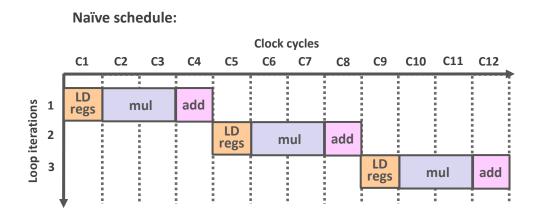

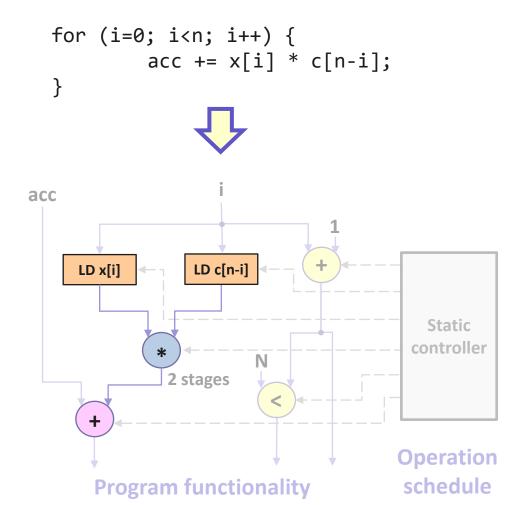

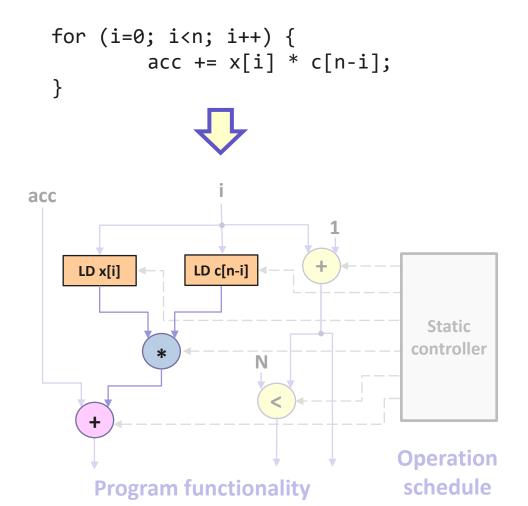

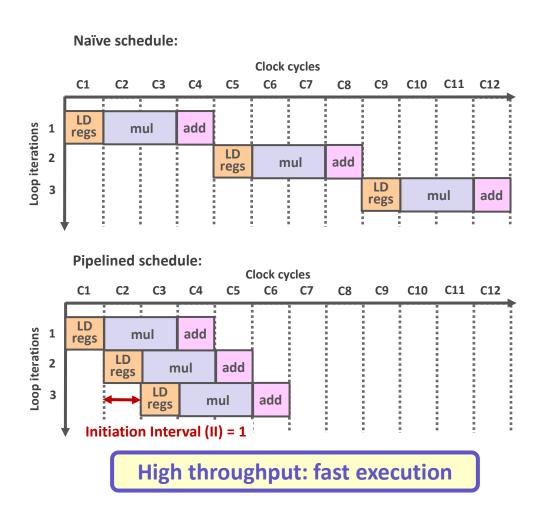

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

- Create a datapath suitable to implement the required computation

- Create a fixed schedule at compile time to activate the datapath components

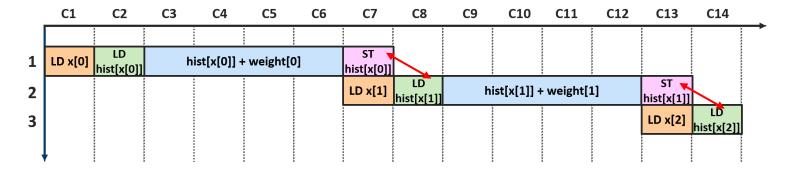

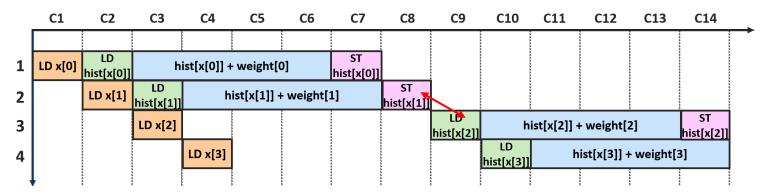

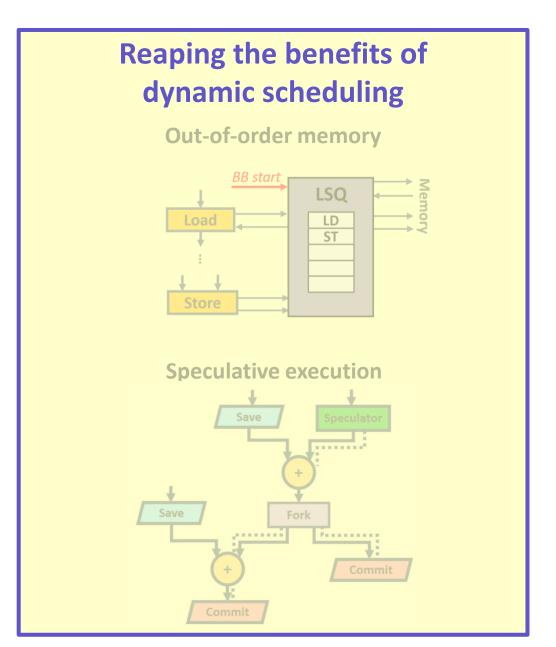

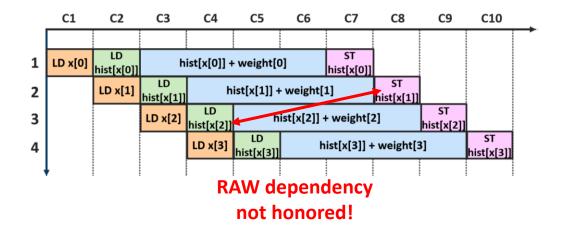

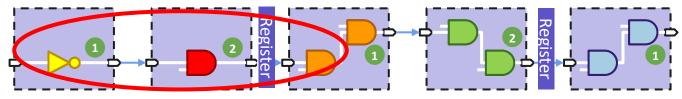

## The Limitations of Static Scheduling

**RAW dependency**

- Static scheduling (standard HLS tool)

- Inferior when memory accesses cannot be disambiguated at compile time

- Dynamic scheduling

- Maximum parallelism: Only serialize memory accesses on actual dependencies

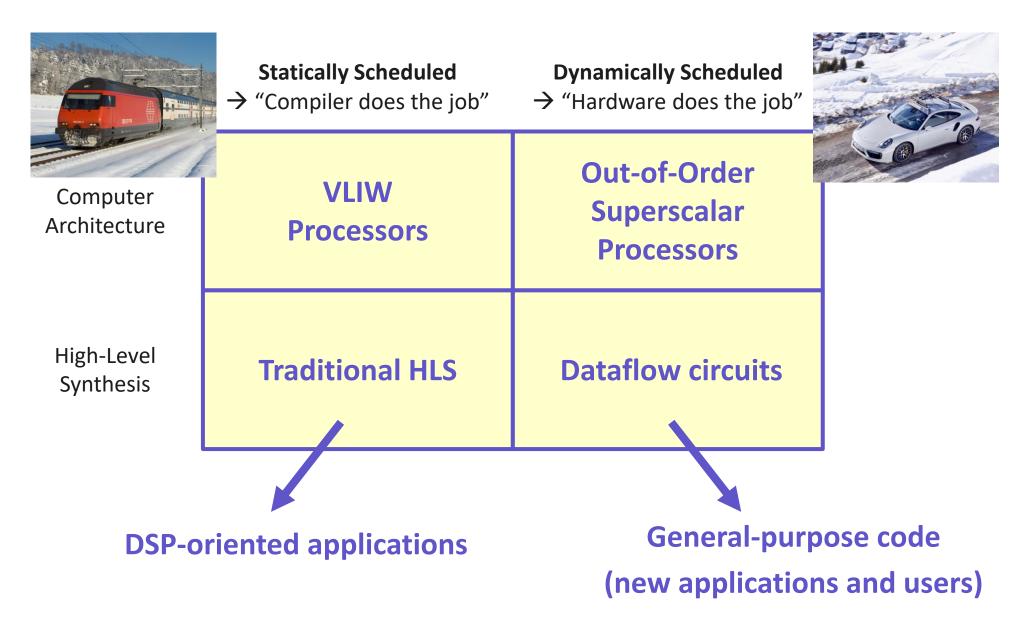

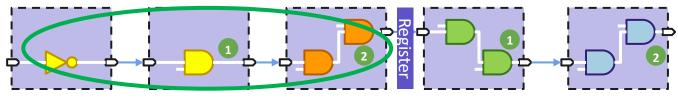

## A Different Way to Do HLS

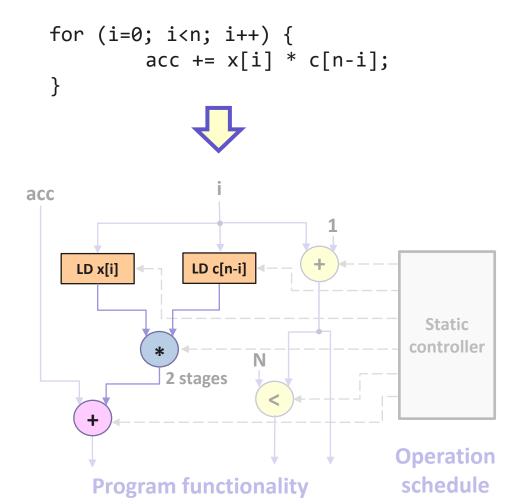

Static scheduling (standard HLS tool): decide at compile time when each operation executes

Dynamic scheduling (our HLS approach): decide at runtime when each operation executes

## A Different Way to Do HLS

Static scheduling (standard HLS tool): decide at compile time when each operation executes

Dynamic scheduling (our HLS approach): decide at runtime when each operation executes

# A Different Way to Do HLS

Static scheduling (standard HLS tool): decide at compile time when each operation executes

Dynamic scheduling (our HLS approach): decide at runtime when each operation executes

## **Dynamically Scheduled Circuits**

- Asynchronous circuits: operators triggered when inputs are available

- Budiu et al. Dataflow: A complement to superscalar. ISPASS'05.

- Dataflow, latency-insensitive, elastic: the synchronous version of it

- Cortadella et al. Synthesis of synchronous elastic architectures. DAC'06.

- Carloni et al. Theory of latency-insensitive design. TCAD'01.

- Jacobson et al. Synchronous interlocked pipelines. ASYNC'02.

- Vijayaraghavan and Arvind. Bounded dataflow networks and latency-insensitive circuits. MEMOCODE'09.

High-level synthesis of dynamically scheduled circuits

# **HLS of Dynamically Scheduled Circuits**

## **HLS of Dynamically Scheduled Circuits**

# **HLS of Dynamically Scheduled Circuits**

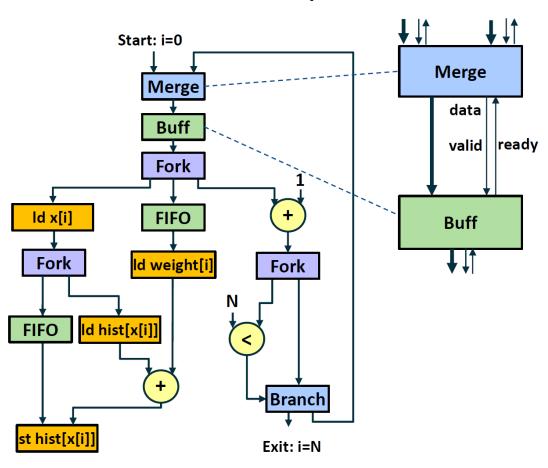

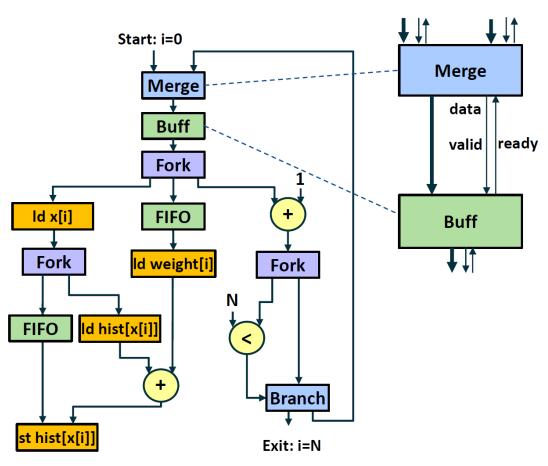

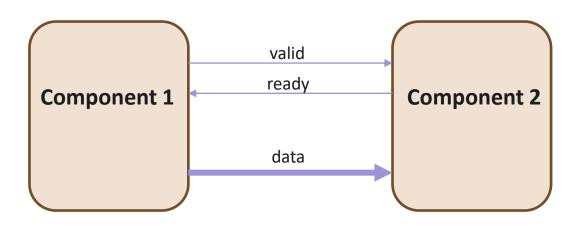

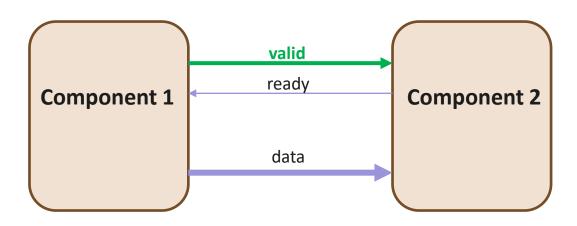

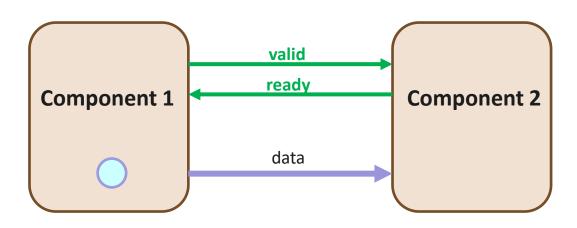

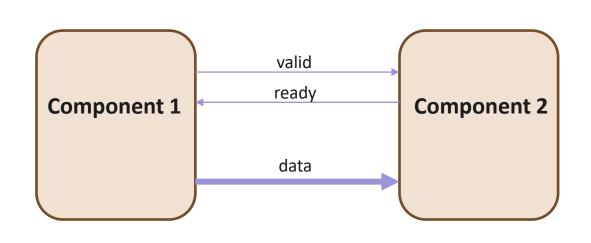

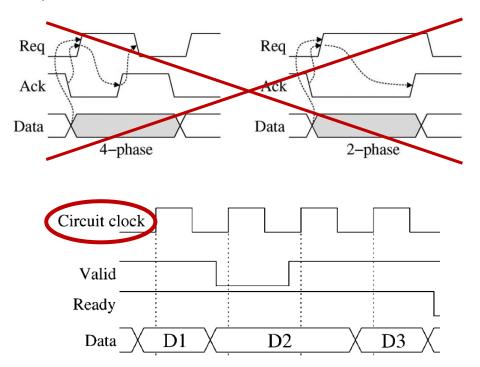

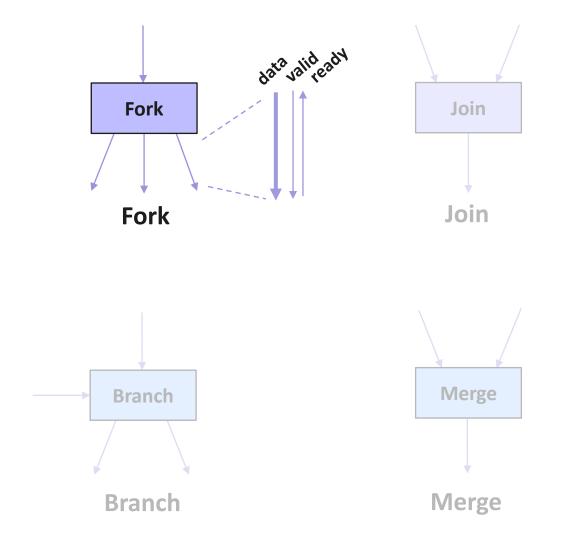

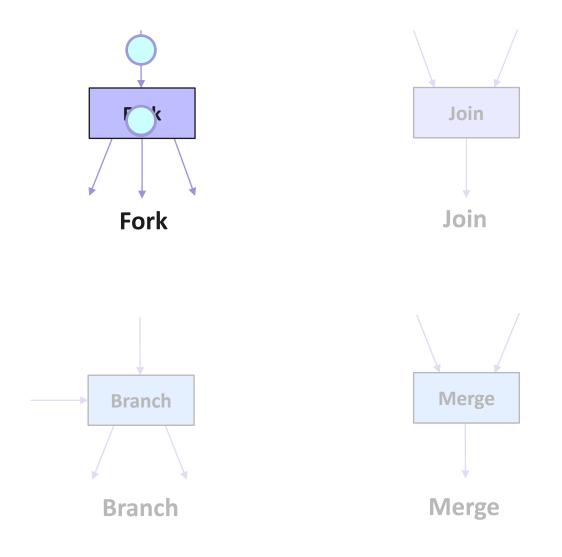

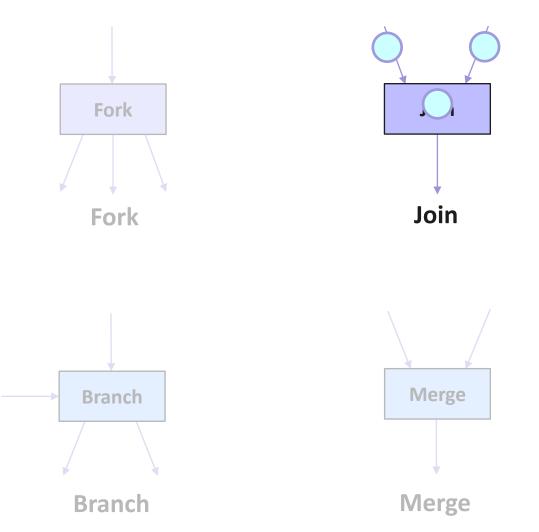

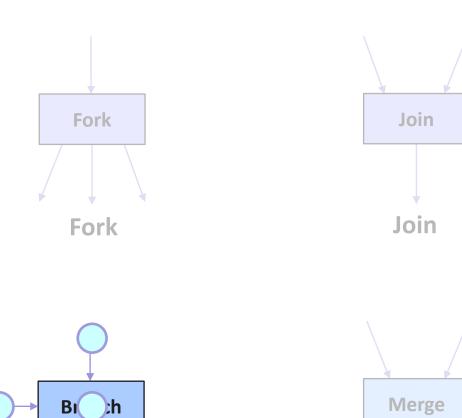

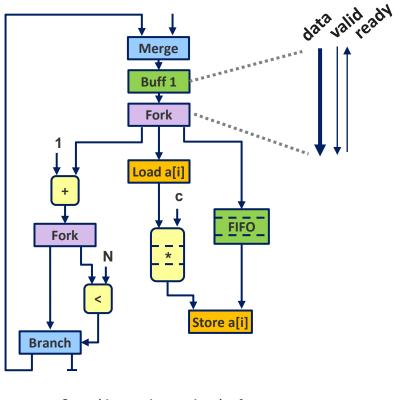

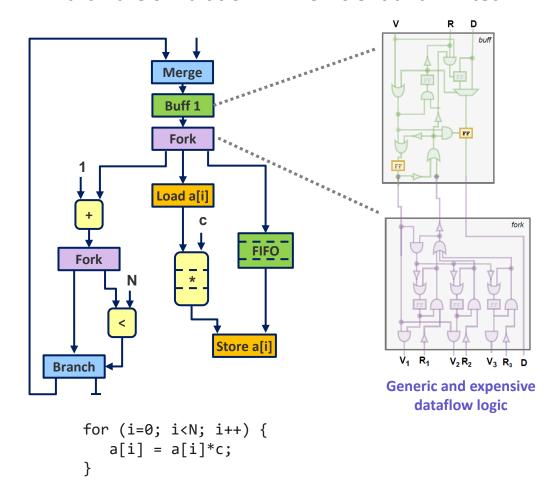

- We use the SELF (Synchronous ELastic Flow) protocol

- Cortadella et al. Synthesis of synchronous elastic architectures. DAC'06.

- Every component communicates via a pair of handshake signals

- Make scheduling decisions at runtime

- As soon as all conditions for execution are satisfied, an operation starts

- We use the SELF (Synchronous ELastic Flow) protocol

- Cortadella et al. Synthesis of synchronous elastic architectures. DAC'06.

- Every component communicates via a pair of handshake signals

- Make scheduling decisions at runtime

- As soon as all conditions for execution are satisfied, an operation starts

- We use the SELF (Synchronous ELastic Flow) protocol

- Cortadella et al. Synthesis of synchronous elastic architectures. DAC'06.

- Every component communicates via a pair of handshake signals

- Make scheduling decisions at runtime

- As soon as all conditions for execution are satisfied, an operation starts

- We use the SELF (Synchronous ELastic Flow) protocol

- Cortadella et al. Synthesis of synchronous elastic architectures. DAC'06.

- Every component communicates via a pair of handshake signals

- Make scheduling decisions at runtime

- As soon as all conditions for execution are satisfied, an operation starts

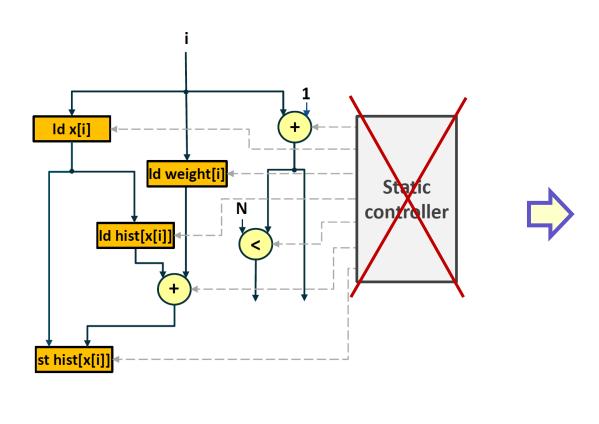

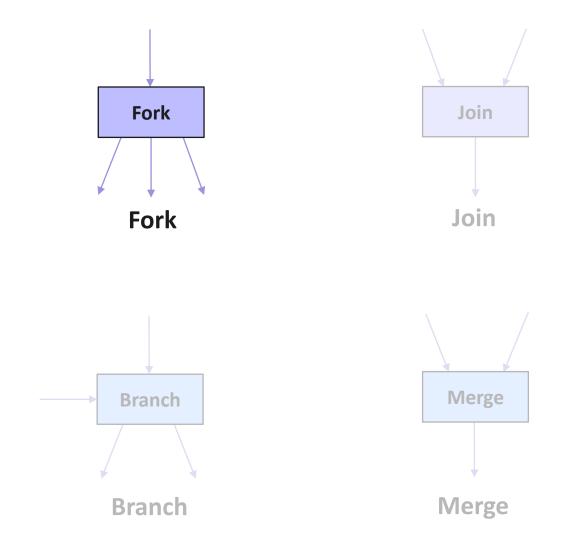

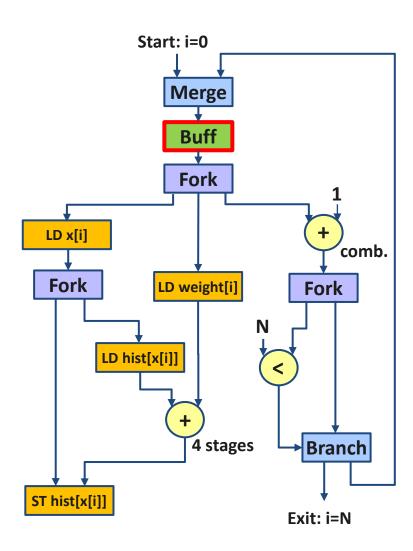

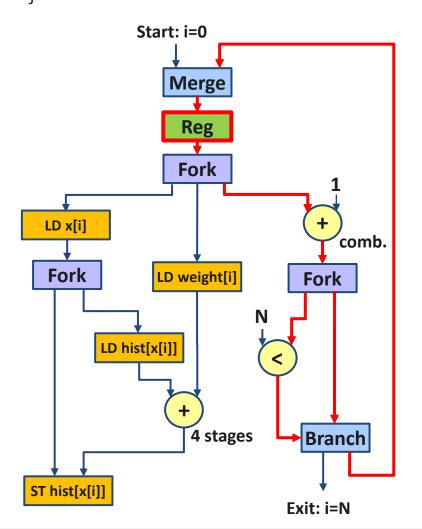

**STORE**

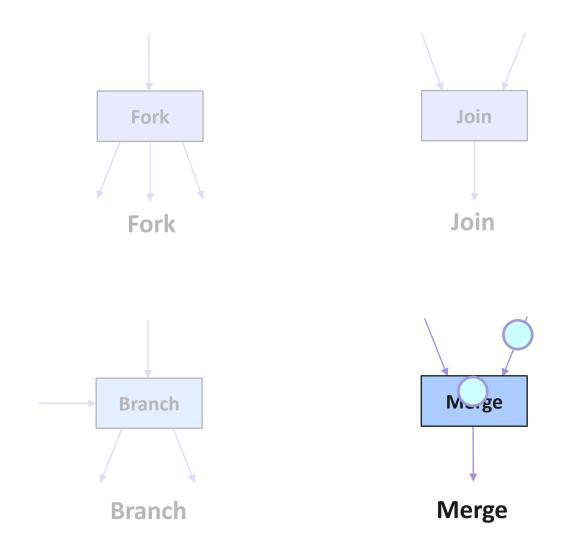

Merge

**Branch**

```

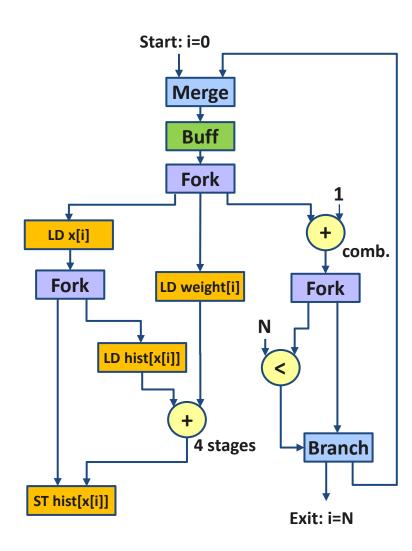

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

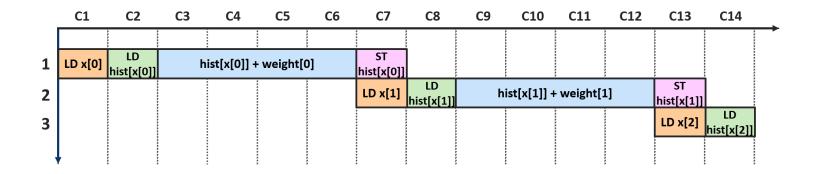

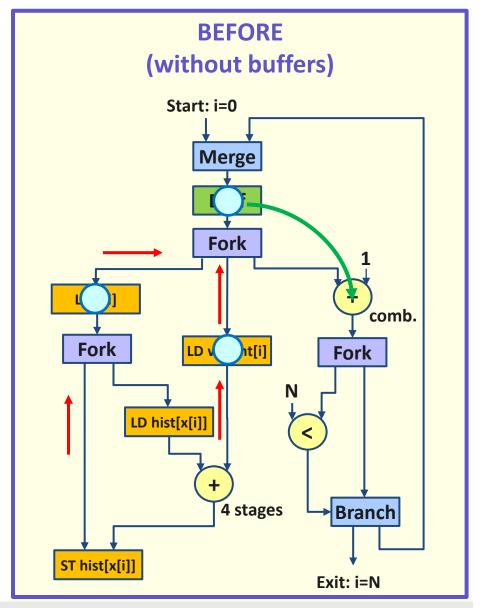

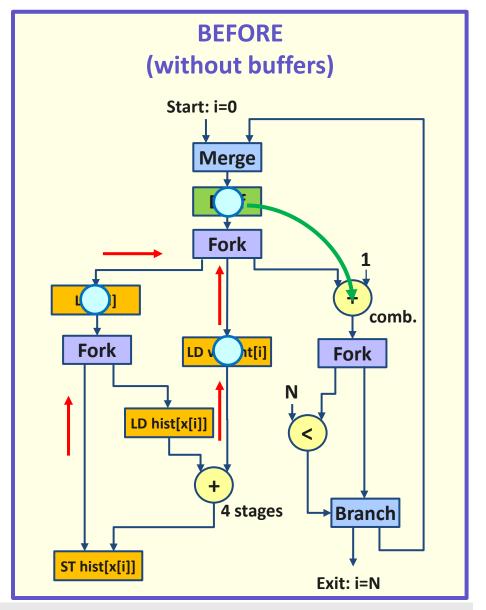

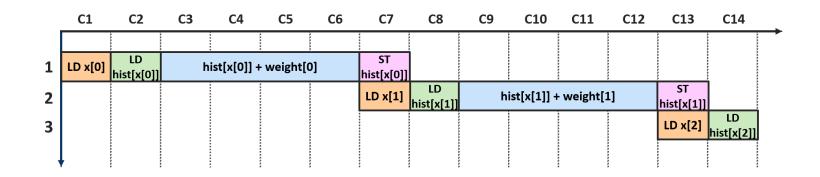

Single token on cycle, in-order tokens in noncyclic paths

Backpressure from slow paths prevents pipelining

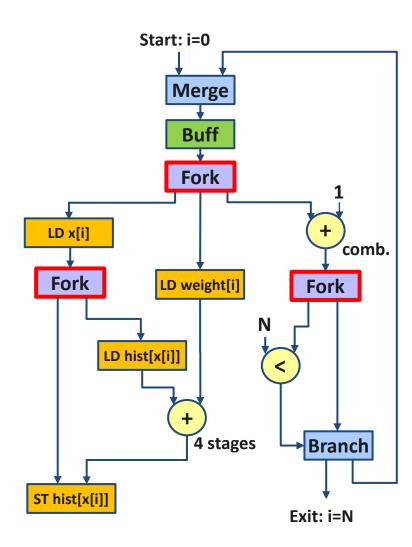

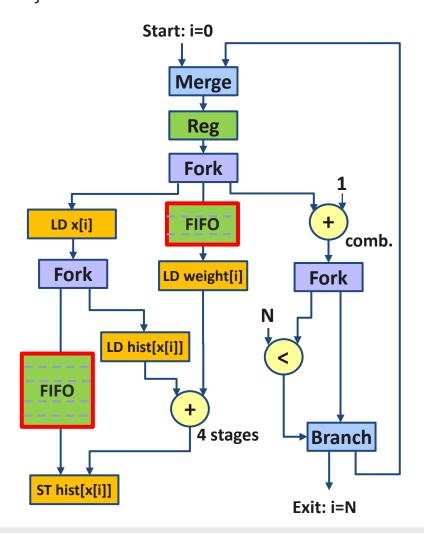

## **HLS of Dynamically Scheduled Circuits**

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

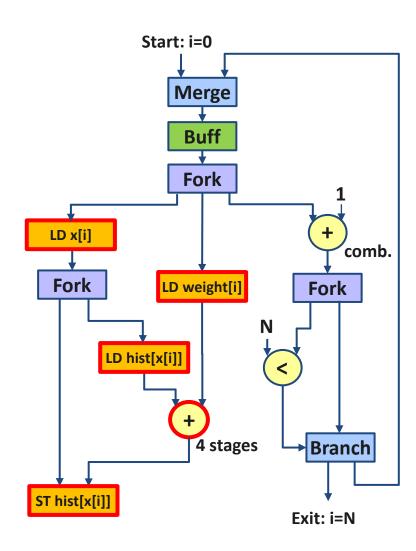

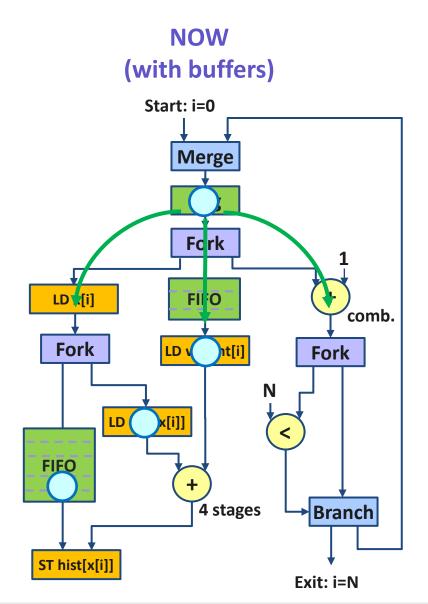

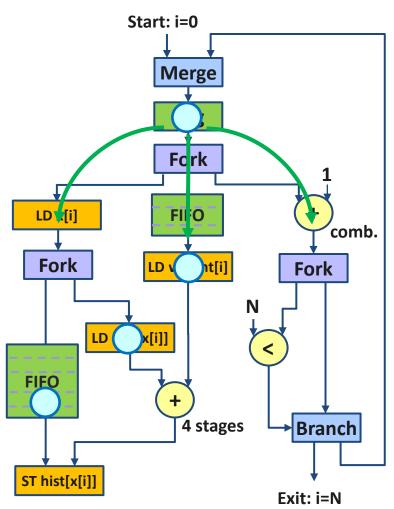

Buffers as registers to break combinational paths

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

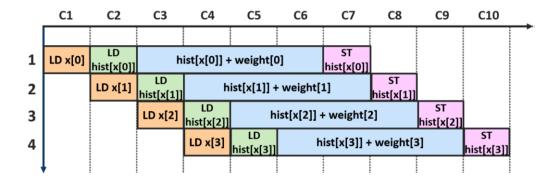

Buffers as FIFOs to regulate throughput

# NOW (with buffers)

Mixed integer linear programming (MILP) model based on **Petri net theory**

- Analyze token flow through the circuit

- Determine buffer placement and sizing

- Maximize throughput for a target clock period

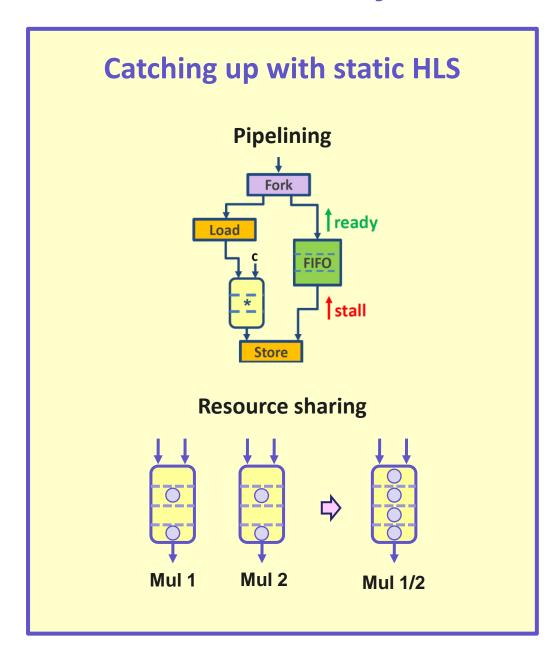

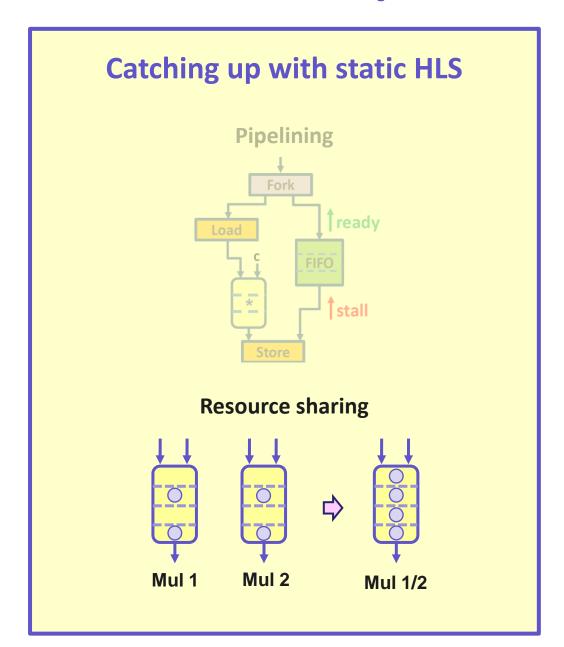

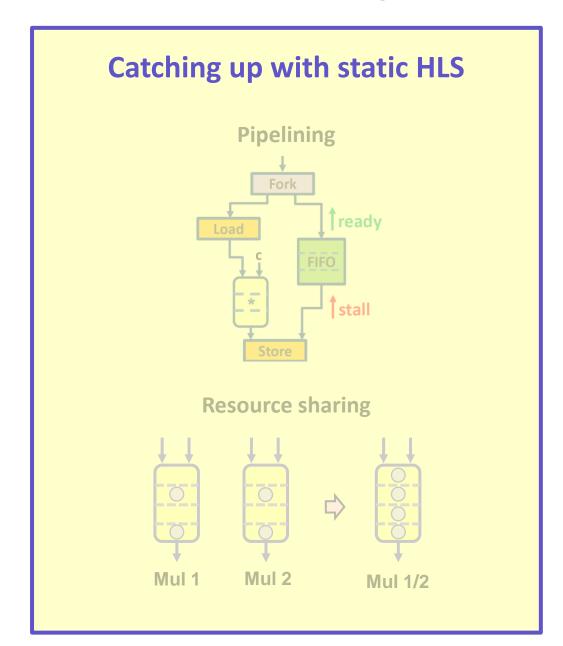

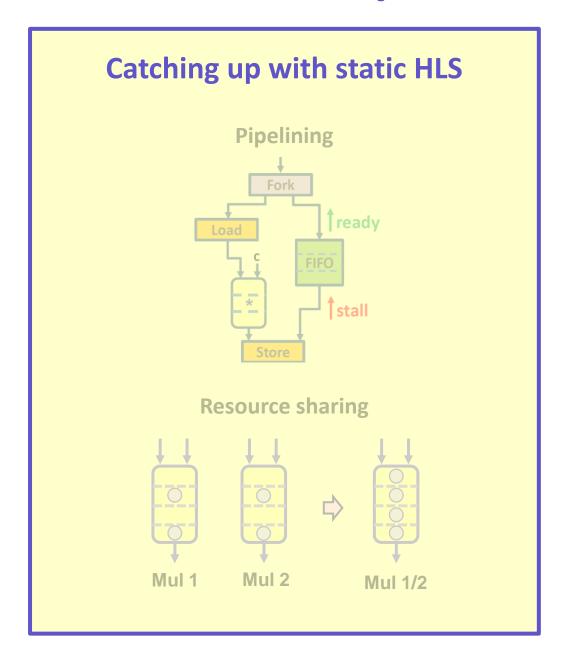

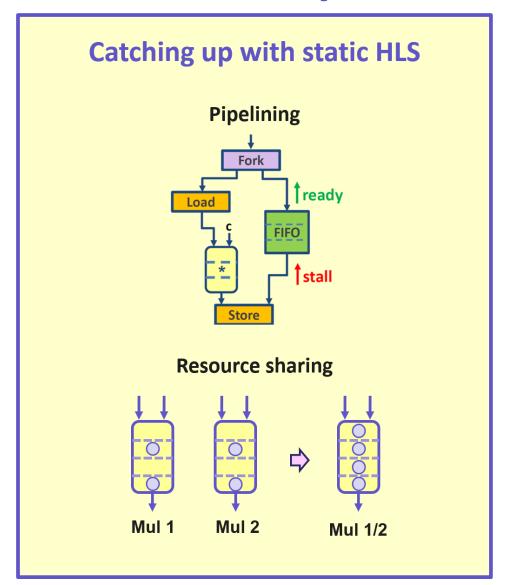

#### **HLS of Dynamically Scheduled Circuits**

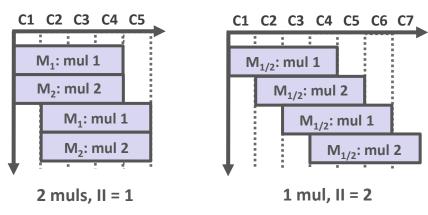

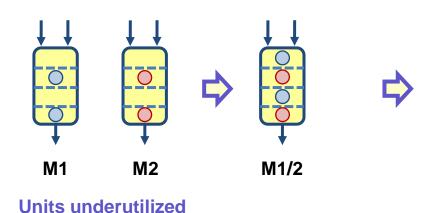

• Static HLS: share units between operations which execute in different clock cycles

```

for (i = 0; i < N; i++) {

a[i] = a[i]*x;

b[i] = b[i]*y;

}</pre>

```

Static HLS: share units between operations which execute in different clock cycles

```

for (i = 0; i < N; i++) {

a[i] = a[i]*x;

b[i] = b[i]*y;

}</pre>

```

#### Static scheduling

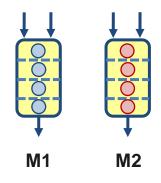

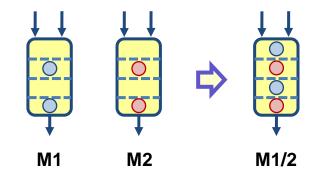

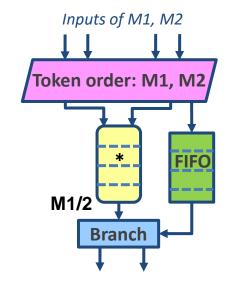

- Static HLS: share units between operations which execute in different clock cycles

- Dynamic HLS: share units based on their average utilization with tokens

```

for (i = 0; i < N; i++) {

a[i] = a[i]*x;

b[i] = b[i]*y;

}</pre>

```

- Static HLS: share units between operations which execute in different clock cycles

- Dynamic HLS: share units based on their average utilization with tokens

```

for (i = 0; i < N; i++) {

a[i] = a[i]*x;

b[i] = b[i]*y;

}</pre>

```

Units fully utilized (high throughput, II = 1)

Sharing not possible without damaging throughput

Use throughput information to decide what to share

- Static HLS: share units between operations which execute in different clock cycles

- Dynamic HLS: share units based on their average utilization with tokens

```

for (i = 0; i < N; i++) {

a[i] = a[i]*x;

b[i] = b[i]*y;

}</pre>

```

Sharing possible without damaging throughput

Units underutilized (low throughput, II = 2)

Use throughput information to decide what to share

- Static HLS: share units between operations which execute in different clock cycles

- Dynamic HLS: share units based on their average utilization with tokens

```

for (i = 0; i < N; i++) {

a[i] = a[i]*x;

b[i] = b[i]*y;

}</pre>

```

(low throughput, II = 2)

**Sharing mechanism for deadlock-free execution**

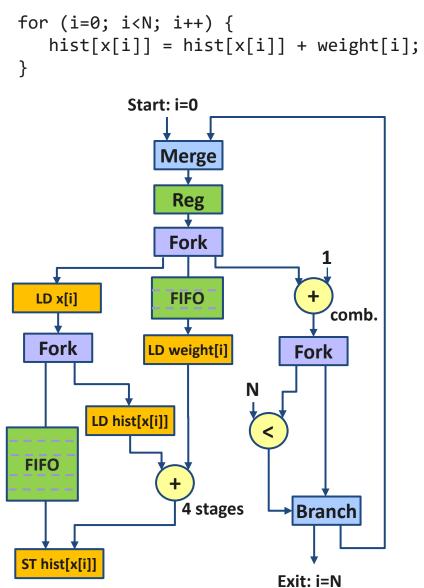

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

Backpressure from slow paths prevents pipelining

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

**Buffers for high throughput**

What about memory?

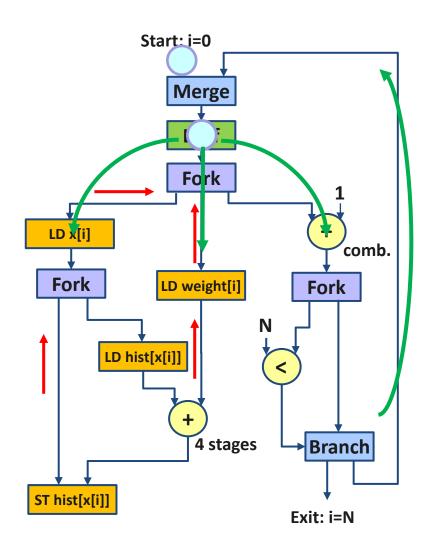

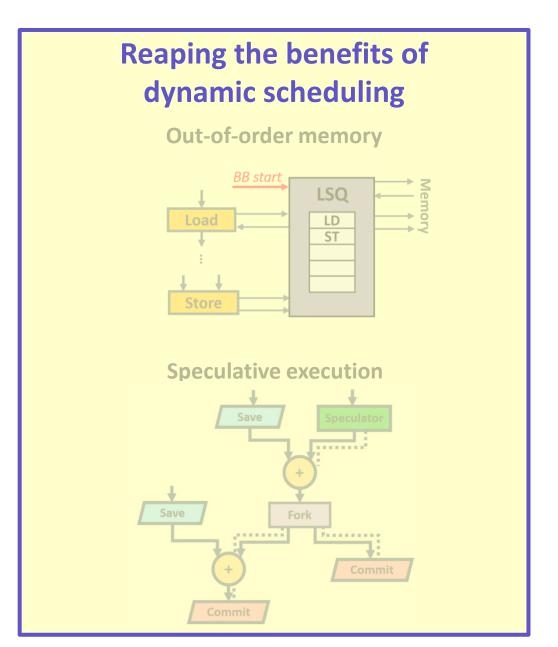

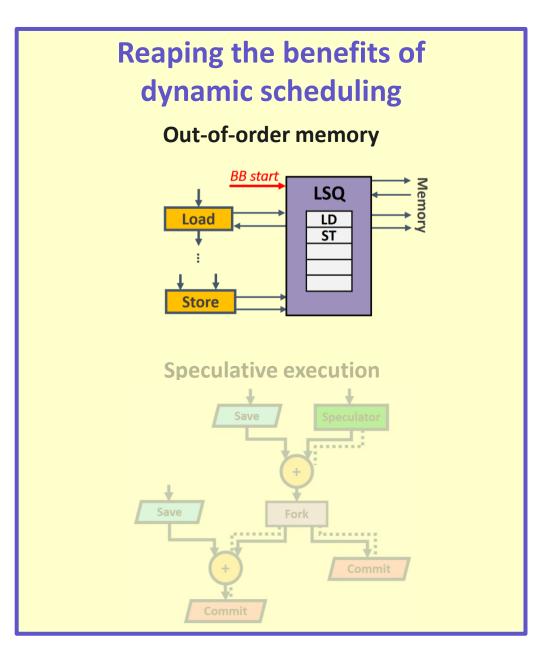

## **HLS of Dynamically Scheduled Circuits**

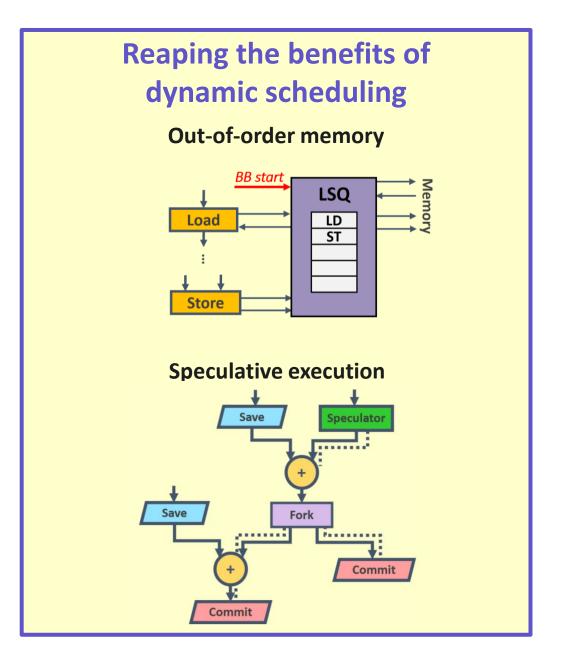

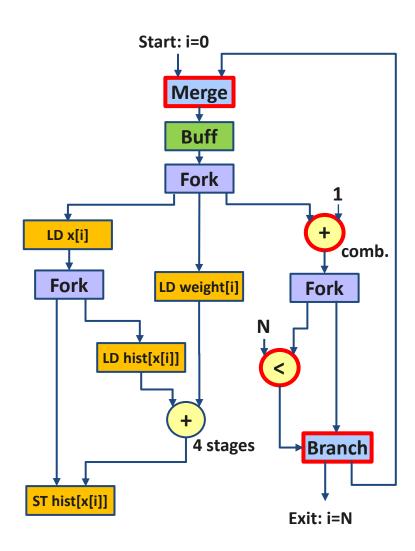

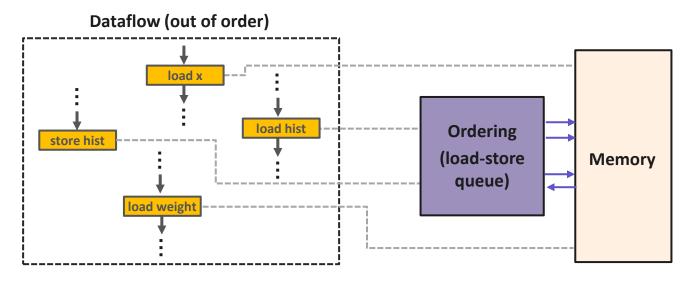

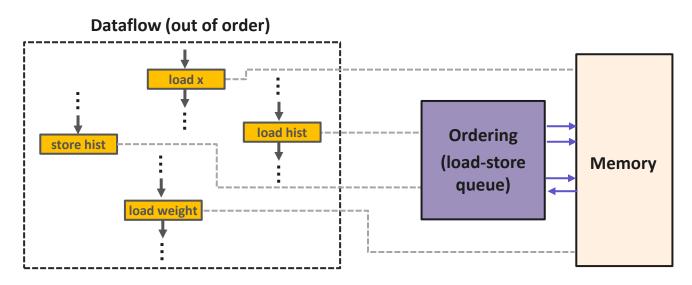

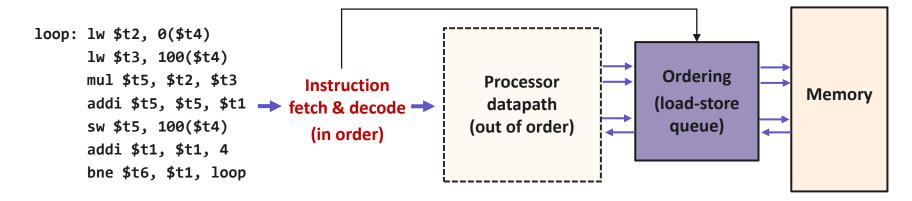

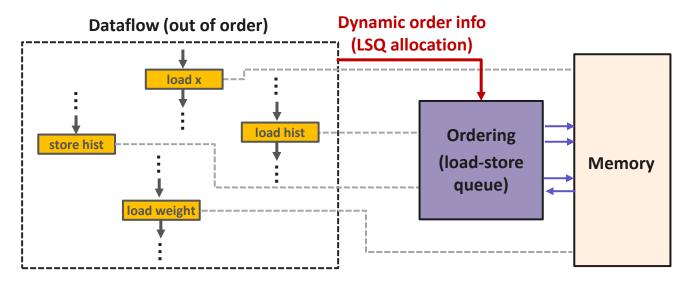

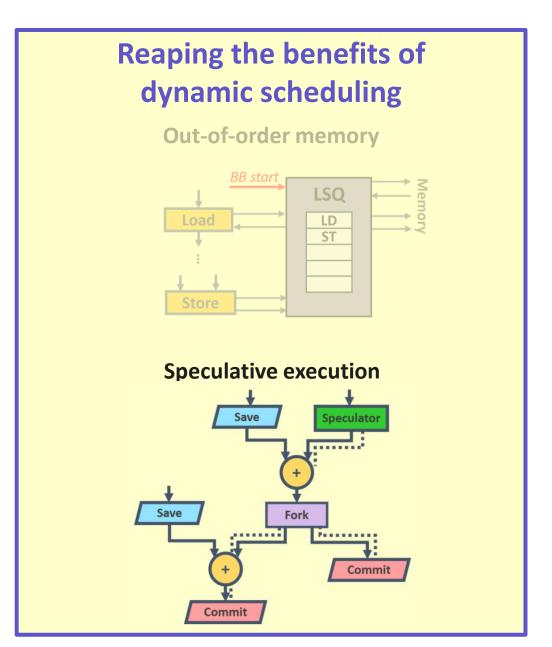

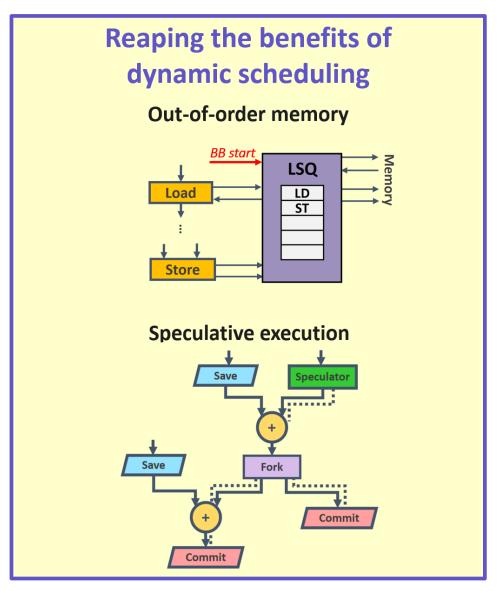

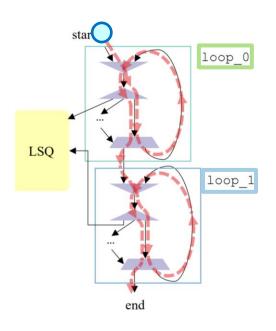

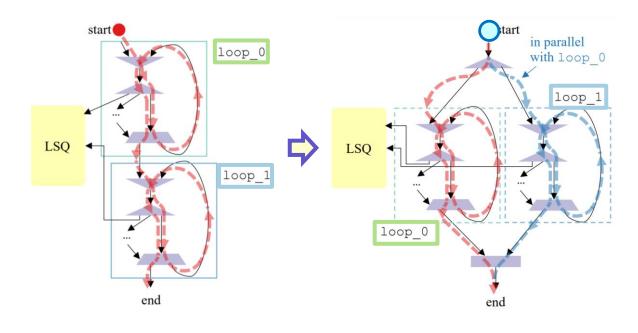

#### **The Ordering Problem**

- A dataflow circuit may reorder memory accesses in (almost) any way

- We need to keep RAWs, WAWs, and WARs in the original program order

RAW = Read after write  $st(n) \rightarrow Id(n)$ WAW = Write after write  $st(n) \rightarrow st(n)$ WAR = Write after read  $Id(n) \rightarrow st(n)$

#### We Need a Load-Store Queue (LSQ)!

• Processor LSQs keep dependent memory accesses in the original program order

#### We Need a Load-Store Queue (LSQ)!

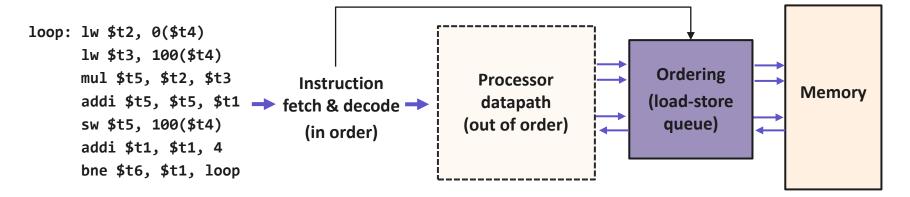

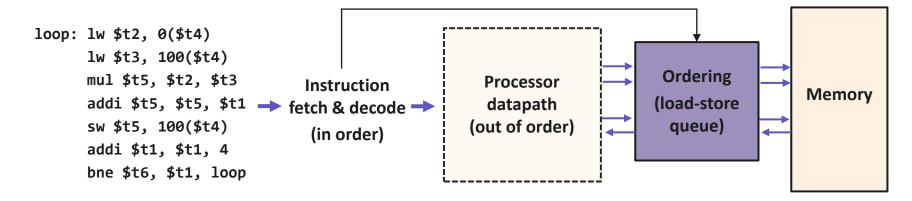

Processor LSQs keep dependent memory accesses in the original program order

Application-specific LSQs for dataflow circuits

#### We Need a Load-Store Queue (LSQ)!

Processor LSQs keep dependent memory accesses in the original program order

```

loop: lw $t2, 0($t4)

lw $t3, 100($t4)

Ordering

mul $t5, $t2, $t3

Processor

Instruction

Memory

addi $t5, $t5, $t1 → fetch & decode →

datapath

(load-store

sw $t5, 100($t4)

(out of order)

queue)

(in order)

addi $t1, $t1, 4

bne $t6, $t1, loop

```

Application-specific LSQs for dataflow circuits

LSQ placement and sizing for high throughput and low resources

```

for (i=0; i<N; i++) {

hist[x[i]] = hist[x[i]] + weight[i];

}</pre>

```

#### We Need a Load-Store Queue (LSQ)!

• Processor LSQs keep dependent memory accesses in the original program order

Application-specific LSQs for dataflow circuits

Memory access ordering info devised by dataflow circuit

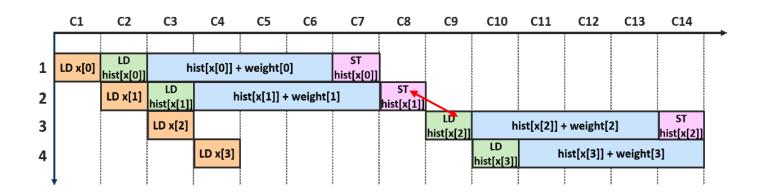

#### **Dataflow Circuit with the LSQ**

High-throughput pipeline with memory dependencies honored

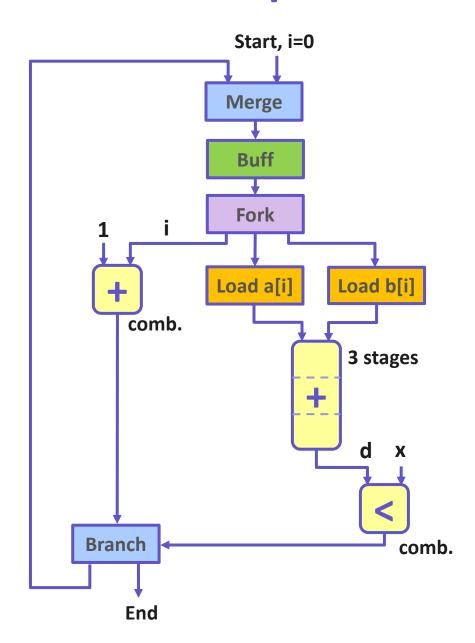

## **HLS of Dynamically Scheduled Circuits**

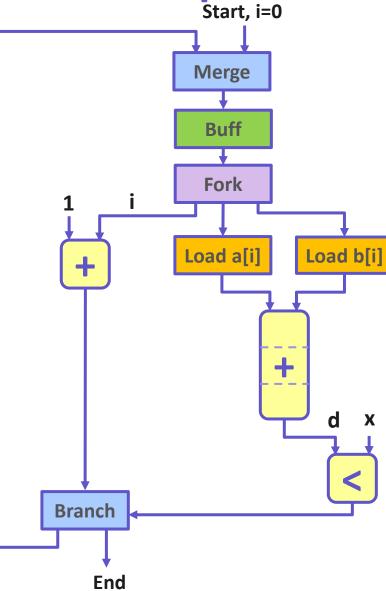

```

float d=0.0; x=100.0; int i=0;

do {

d = a[i] + b[i];

i++;

}

while (d<x);</pre>

```

```

float d=0.0; x=100.0; int i=0;

do {

d = a[i] + b[i];

i++;

}

while (d<x);</pre>

```

```

float d=0.0; x=100.0; int i=0;

do {

d = a[i] + b[i];

i++;

}

while (d<x);</pre>

```

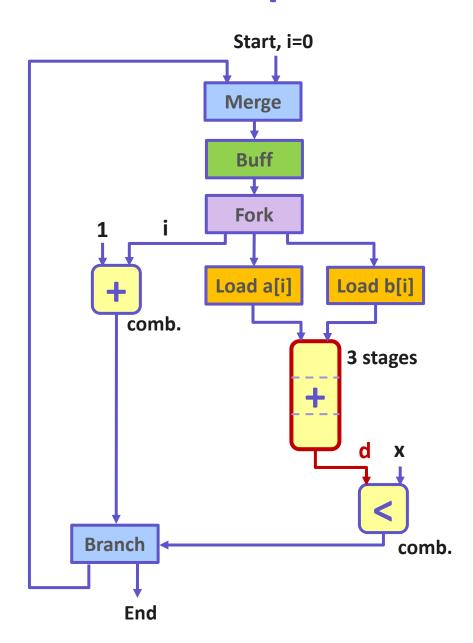

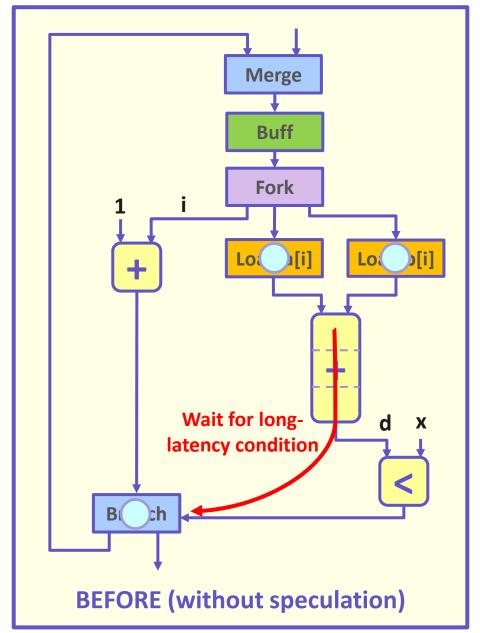

#### Nonspeculative vs. Speculative System

```

float d=0.0; x=100.0; int i=0;

1: a[0]=50.0; b[0]=30.0

2: a[1]=40.0; b[1]=40.0

do {

3: a[2]=50.0; b[2]=60.0 \rightarrow exit

d = a[i] + b[i];

i++;

while (d<x);

Nonspeculative schedule

C1

C5

C6

C7

C10

C11

C12

C13

C14

C15

C16

C8

C9

ld a[0]

d1 = a[0] + b[0]

d1<x?

ld b[0]

ld a[1]

d2 = a[1] + b[1]

d2<x?

2

ld b[1]

ld a[2]

d3 = a[2] + b[2]

d3<x?

exit

3

ld b[2]

```

Long control flow decision prevents pipelining

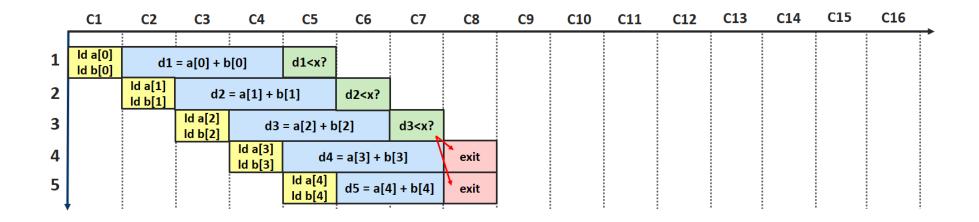

#### Nonspeculative vs. Speculative System

```

float d=0.0; x=100.0; int i=0;

1: a[0]=50.0; b[0]=30.0

2: a[1]=40.0; b[1]=40.0

do {

3: a[2]=50.0; b[2]=60.0 \rightarrow exit

d = a[i] + b[i];

i++;

while (d<x);

Nonspeculative schedule

C1

C2

C5

C6

C7

C10

C11

C12

C13

C14

C15

C16

C8

C9

ld a[0]

d1 = a[0] + b[0]

d1<x?

ld b[0]

ld a[1]

d2 = a[1] + b[1]

d2<x?

2

ld b[1]

ld a[2]

d3 = a[2] + b[2]

d3<x?

exit

3

ld b[2]

4

Speculative schedule

C15

C13

C14

C16

C2

C3

C5

C6

C7

C8

C9

C10

C11

C12

ld a[0]

d1 = a[0] + b[0]

d1<x?

ld b[0]

ld a[1]

2

d2 = a[1] + b[1]

d2<x?

ld b[1]

ld a[2]

3

d3 = a[2] + b[2]

d3<x?

ld b[2]

ld a[3]

d4 = a[3] + b[3]

exit

ld b[3]

5

d5 = a[4] + b[4]

exit

```

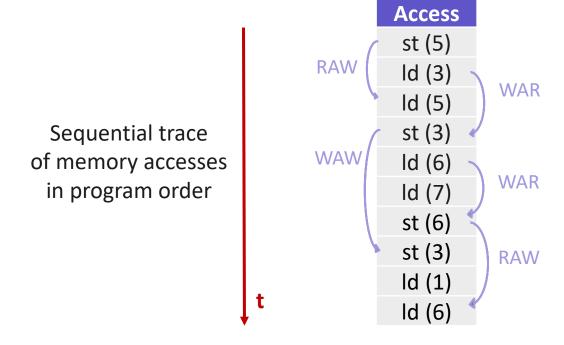

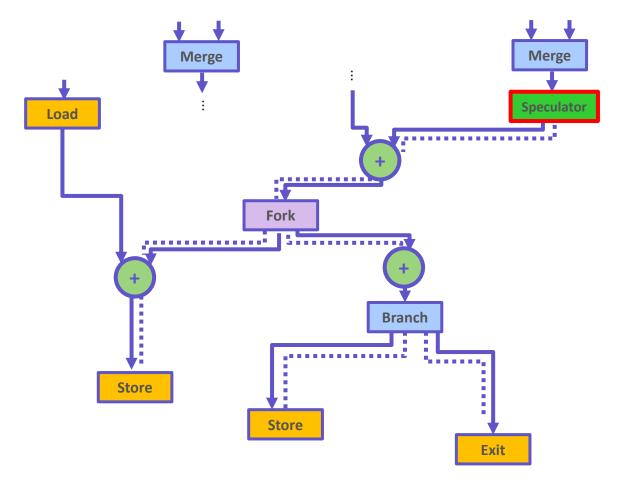

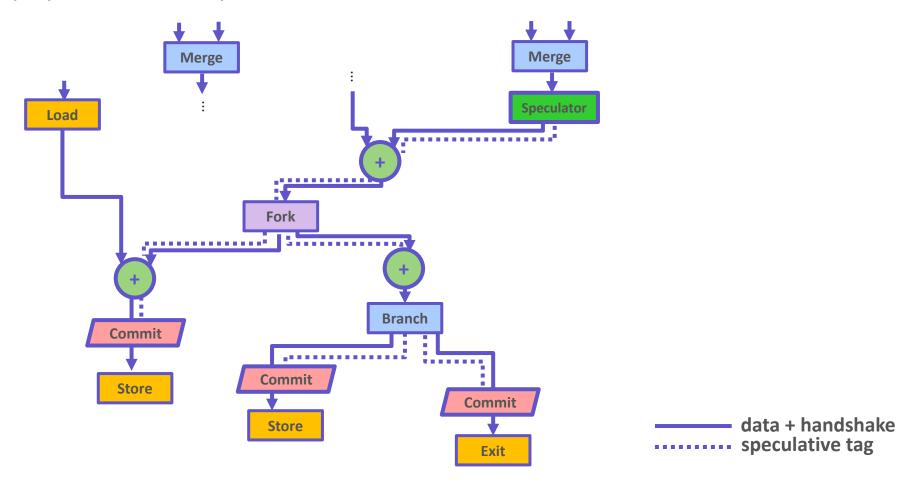

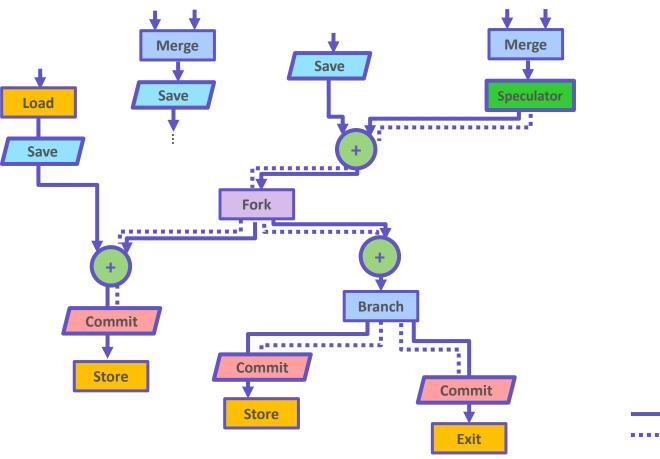

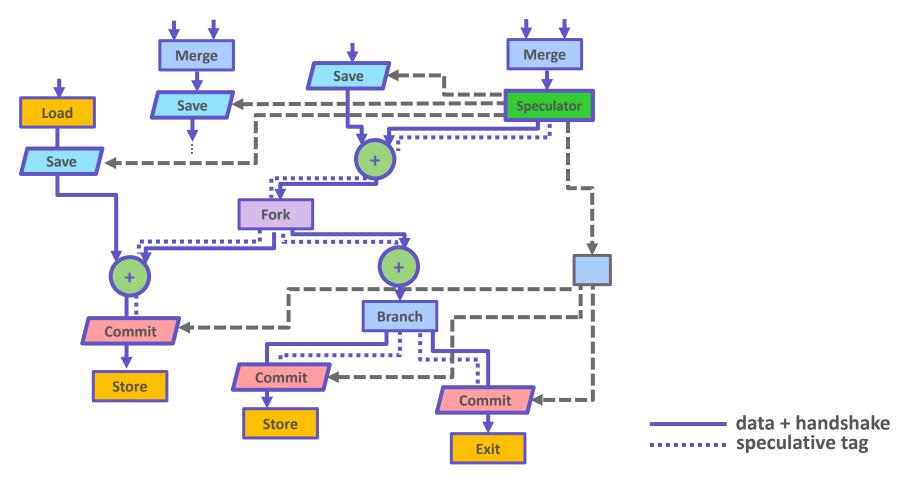

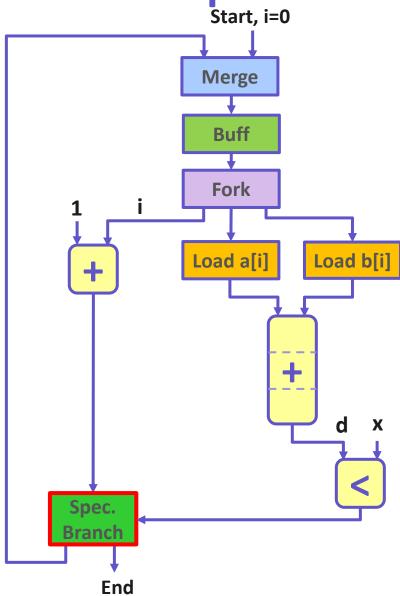

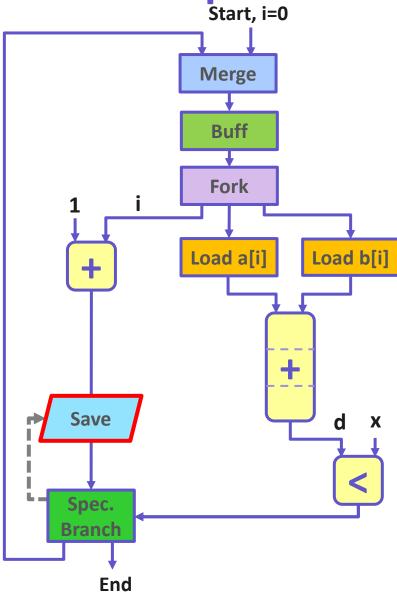

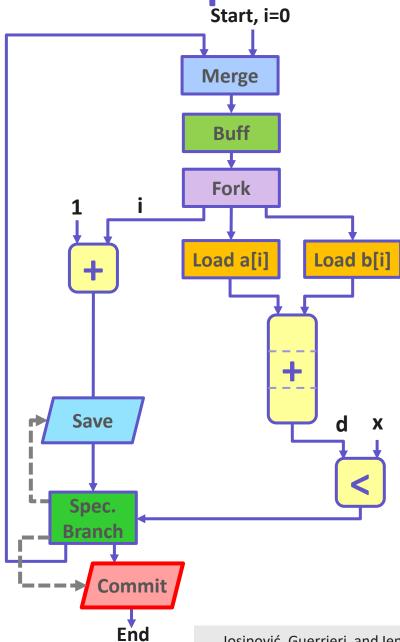

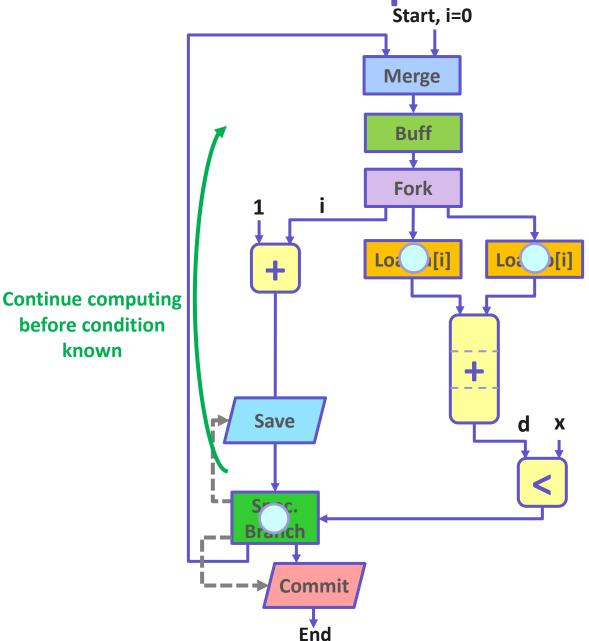

- Contain speculation in a region of the circuit delimited by special components

- Issue speculative tokens (pieces of data which might or might not be correct)

- Squash and replay in case of misspeculation

data + handshake speculative tag

- Contain speculation in a region of the circuit delimited by special components

- Issue speculative tokens (pieces of data which might or might not be correct)

- Squash and replay in case of misspeculation

- Contain speculation in a region of the circuit delimited by special components

- Issue speculative tokens (pieces of data which might or might not be correct)

- Squash and replay in case of misspeculation

data + handshake speculative tag

- Contain speculation in a region of the circuit delimited by special components

- Issue speculative tokens (pieces of data which might or might not be correct)

- Squash and replay in case of misspeculation

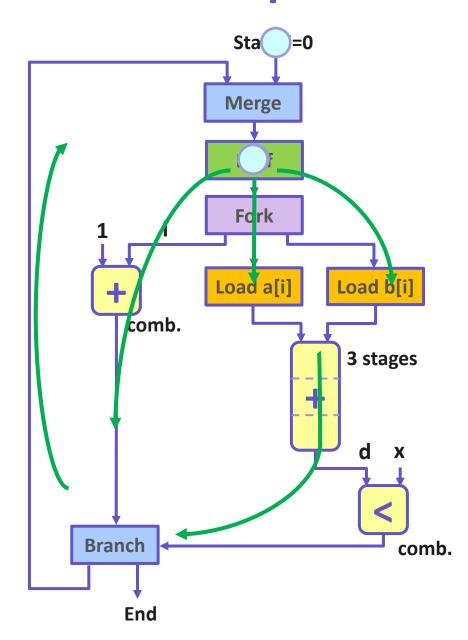

# **Speculative Dataflow Circuit** Start, i=0

Speculator instead of regular Branch

# Speculative Dataflow Circuit Start, i=0

**Input boundary: Save units**

Output boundary: Commit units

known

High-throughput speculative pipeline

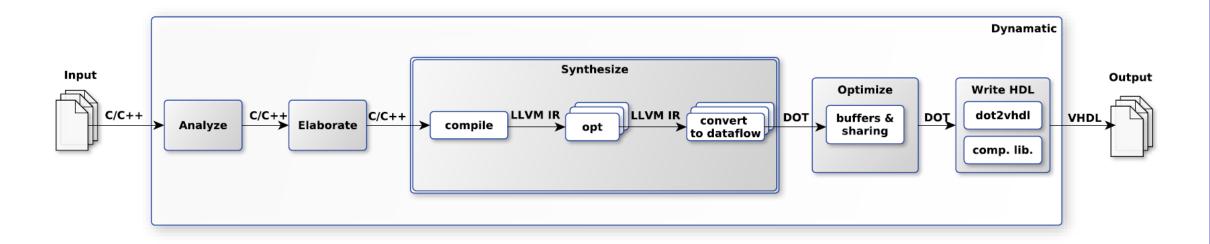

#### **HLS of Dynamically Scheduled Circuits**

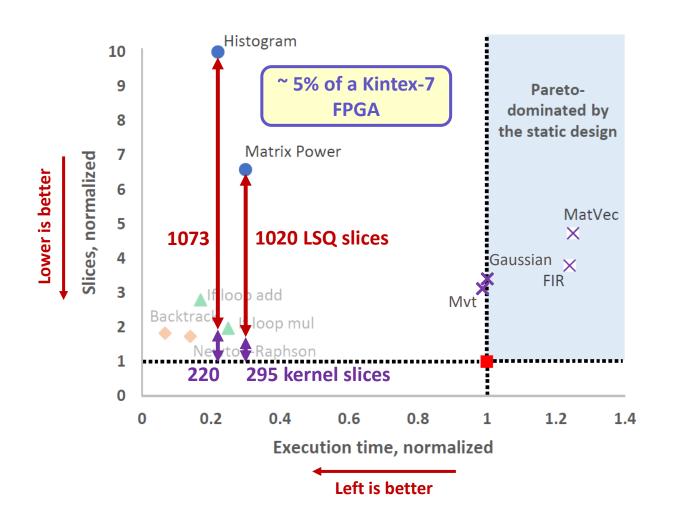

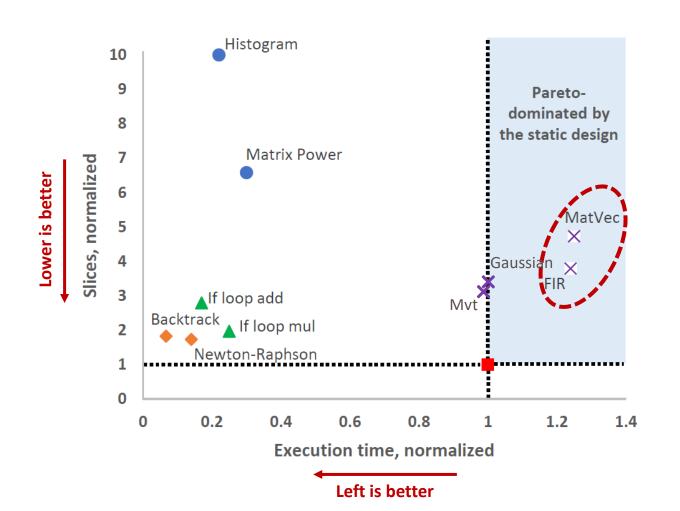

Dynamatic: an open-source HLS compiler

- Dynamatic: an open-source HLS compiler

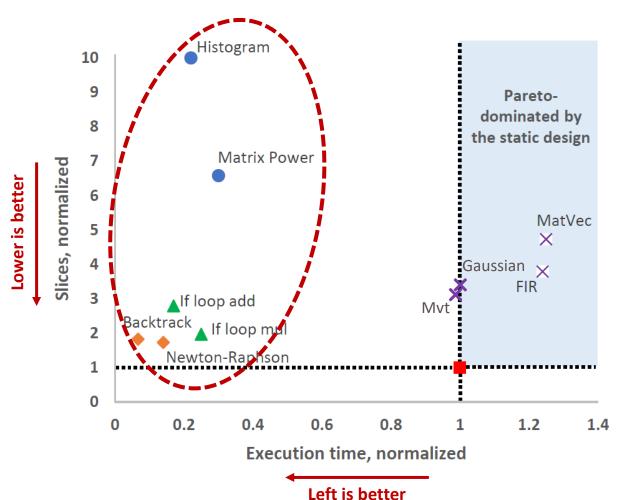

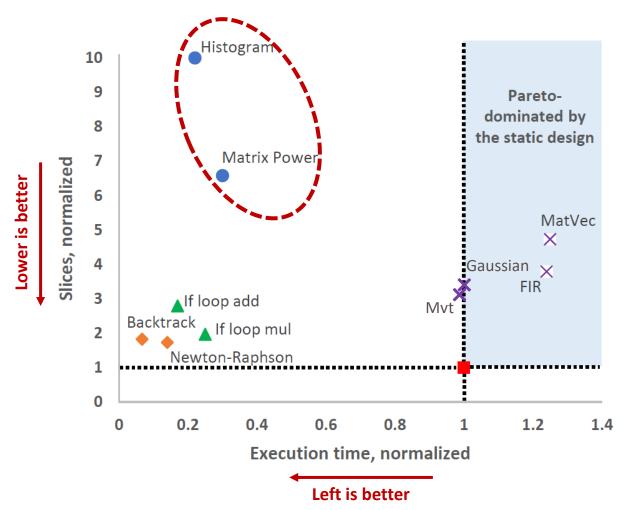

- Resource utilization and execution time of the dataflow designs, normalized to the corresponding static designs produced by Vivado HLS

- ▲ Dynamic, control dependences

- Dynamic, memory dependences

- Dynamic, speculative

- imes Dynamic, no dependences

- Static (all points)

- Dynamatic: an open-source HLS compiler

- Resource utilization and execution time of the dataflow designs, normalized to the corresponding static designs produced by Vivado HLS

- ▲ Dynamic, control dependences

- Dynamic, memory dependences

- Dynamic, speculative

- X Dynamic, no dependences

- Static (all points)

Reduced execution time in irregular benchmarks (speedup of up to 14.9X)

- Dynamatic: an open-source HLS compiler

- Resource utilization and execution time of the dataflow designs, normalized to the corresponding static designs produced by Vivado HLS

- ▲ Dynamic, control dependences

- Dynamic, memory dependences

- Dynamic, speculative

- X Dynamic, no dependences

- Static (all points)

Reduced execution time in irregular benchmarks (speedup of up to 14.9X)

- Dynamatic: an open-source HLS compiler

- Resource utilization and execution time of the dataflow designs, normalized to the corresponding static designs produced by Vivado HLS

- ▲ Dynamic, control dependences

- Dynamic, memory dependences

- Dynamic, speculative

- X Dynamic, no dependences

- Static (all points)

LSQ causes significant resource overheads

- Dynamatic: an open-source HLS compiler

- Resource utilization and execution time of the dataflow designs, normalized to the corresponding static designs produced by Vivado HLS

- ▲ Dynamic, control dependences

- Dynamic, memory dependences

- Dynamic, speculative

- X Dynamic, no dependences

- Static (all points)

LSQ causes significant resource overheads

- Dynamatic: an open-source HLS compiler

- Resource utilization and execution time of the dataflow designs, normalized to the corresponding static designs produced by Vivado HLS

- ▲ Dynamic, control dependences

- Dynamic, memory dependences

- Dynamic, speculative

- X Dynamic, no dependences

- Static (all points)

Static and dynamic HLS have the same pipelining capabilities

- Dynamatic: an open-source HLS compiler

- Resource utilization and execution time of the dataflow designs, normalized to the corresponding static designs produced by Vivado HLS

- ▲ Dynamic, control dependences

- Dynamic, memory dependences

- Dynamic, speculative

- X Dynamic, no dependences

- Static (all points)

Regular benchmarks are Pareto-dominated due to CP increase

### Static vs. Dynamic Scheduling

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

A different way to go about HLS (generating dynamically scheduled circuits from C code)

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

Sequential C-based synthesis still limits achievable parallelism

#### SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

## Sequential C-based synthesis still limits achievable parallelism

New programming models and compiler techniques for irregular parallelism

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

Functional verification of HLS circuits using hardware simulation → inefficient and limited

HW

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

Functional verification of HLS circuits using hardware simulation → inefficient and limited

HW

SW

**HLS** is still not meant for software programmers

**HLS often fails in extracting** parallelism from software code

**HLS** circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

**Functional verification** of HLS circuits using hardware simulation  $\rightarrow$  inefficient and limited

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

Functional verification of HLS circuits using hardware simulation → inefficient and limited

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

Functional verification of HLS circuits using hardware simulation → inefficient and limited

A formal verification framework for improving the quality of circuits generated from software code

SW

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

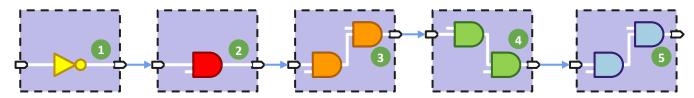

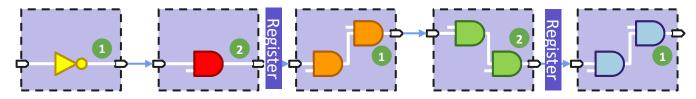

Standard pipelining (register placement) is unaware of circuit transformations during logic synthesis and technology mapping

Standard pipelining (target: 2 logic levels after 3-LUT mapping)

**SW**

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

Standard pipelining (register placement) is unaware of circuit transformations during logic synthesis and technology mapping

Standard pipelining (target: 2 logic levels after 3-LUT mapping)

**SW**

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

Standard pipelining (register placement) is unaware of circuit transformations during logic synthesis and technology mapping

Standard pipelining (target: 2 logic levels after 3-LUT mapping)

Single logic level after logic synthesis → redundant regs, high latency, low frequency

**HW**

**SW**

HLS is still not meant for software programmers

HLS often fails in extracting parallelism from software code

HLS circuits need hardware-level functional verification

It is difficult for HLS to account for reconfigurable platform details

Standard pipelining (register placement) is unaware of circuit transformations during logic synthesis and technology mapping

Standard pipelining (target: 2 logic levels after 3-LUT mapping)

Single logic level after logic synthesis → redundant regs, high latency, low frequency

Simultaneous pipelining & technology mapping (our work)

Fewer registers, low latency, high frequency

Implementation-aware compiler optimizations for fast and small circuits

**HW**

#### Thanks!

#### Research group:

dynamo.ethz.ch

#### **Dynamatic HLS tool:**

dynamatic.epfl.ch

**Dynamatic 2.0 coming soon!**