#### Fine Grain Reconfiguration: the ARTICo<sup>3</sup> Framework

Alfonso Rodríguez

Universidad Politécnica de Madrid

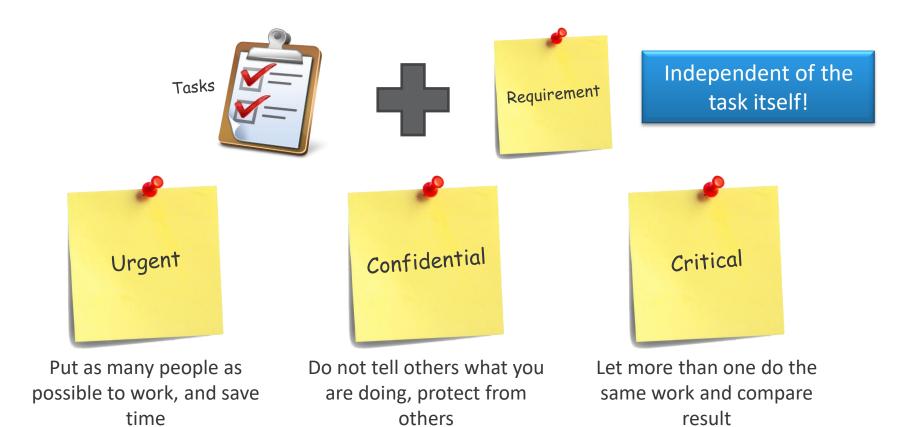

Independent of the task itself!

Independent of the task itself!

Put as many people as possible to work, and save time

#### Replicate xN

Multithreaded solutions HPC-like approach

Independent of the task itself!

Put as many people as possible to work, and save time

#### Replicate xN

Multithreaded solutions HPC-like approach

Do not tell others what you are doing, protect from others

#### **Duplicate**

Dual-rail techniques for sidechannel attack protection

Independent of the task itself!

Put as many people as possible to work, and save time

#### Replicate xN

Multithreaded solutions HPC-like approach

Do not tell others what you are doing, protect from others

#### **Duplicate**

Dual-rail techniques for sidechannel attack protection

Let more than one do the same work and compare result

#### Replicate x2 or x3

(+ voter unit) DMR and TMR

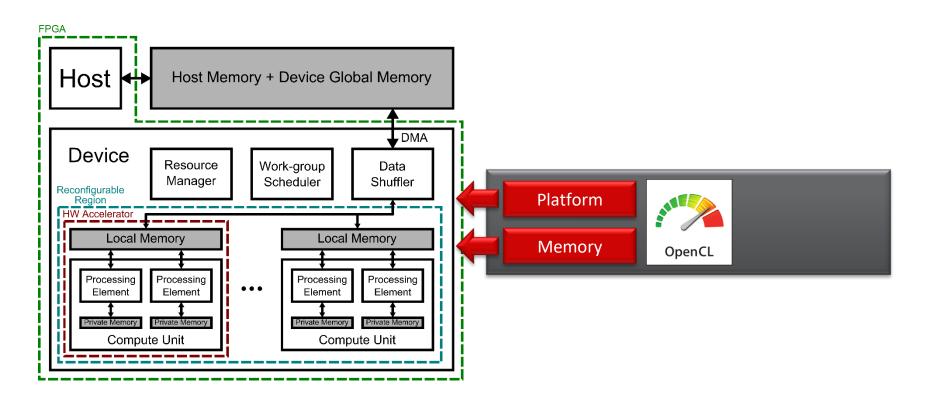

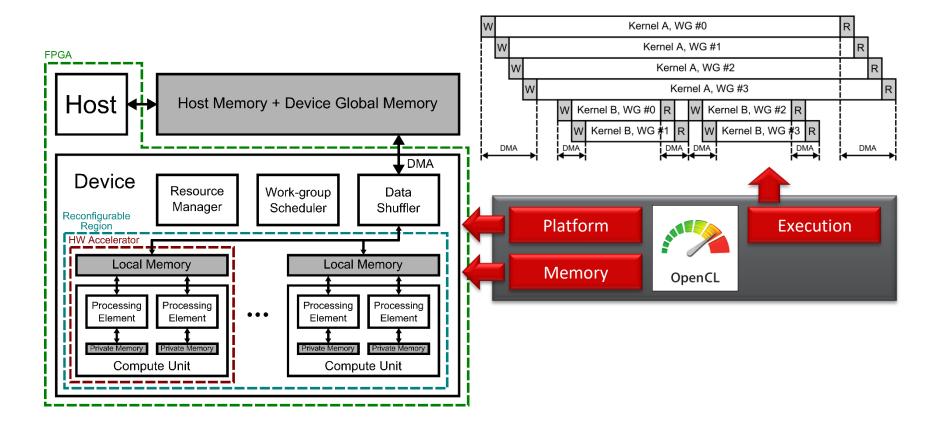

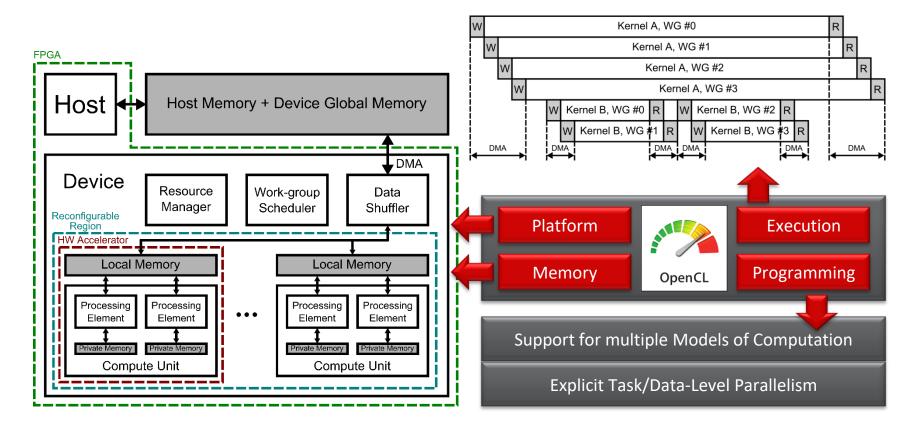

Dynamic and Partial Reconfiguration (hardware acceleration + module replication)

# What is required?

# High Performance Embedded Computing Platforms

#### Architectures

## What is required?

# High Performance Embedded Computing Platforms

### What is required?

# High Performance Embedded Computing Platforms

#### Architectures

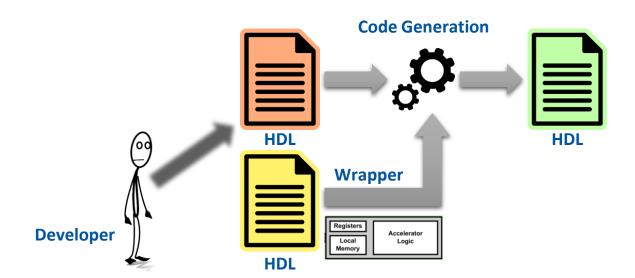

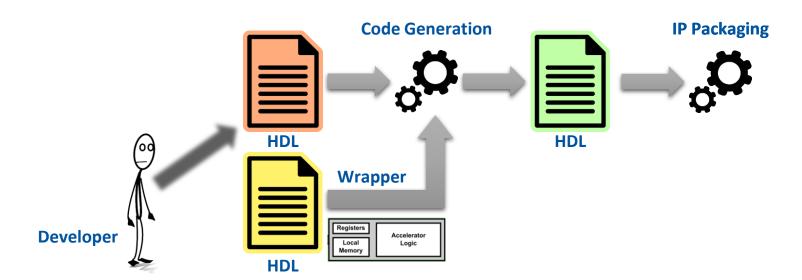

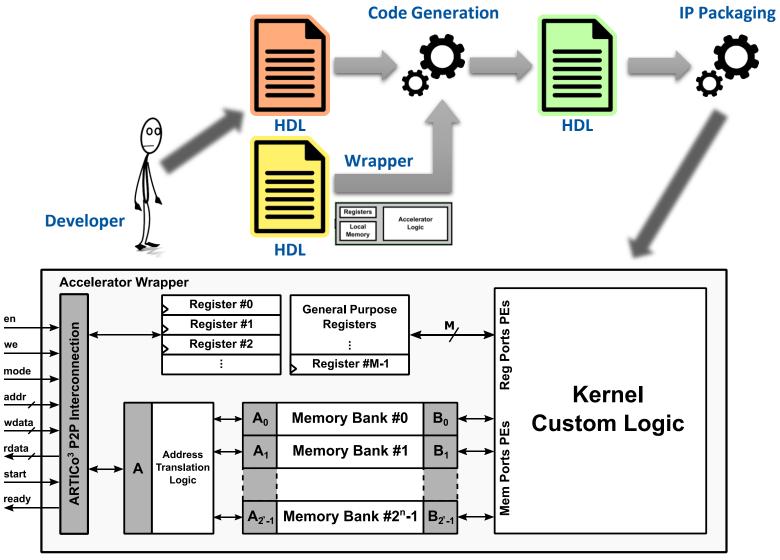

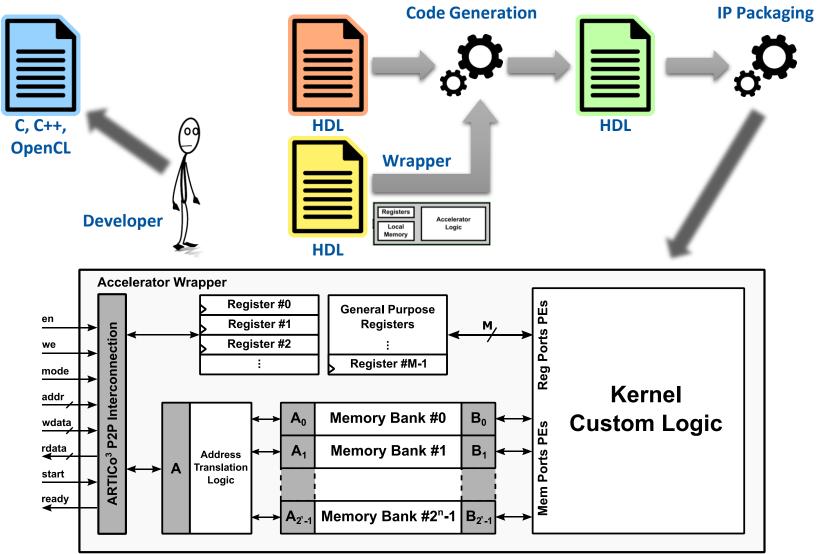

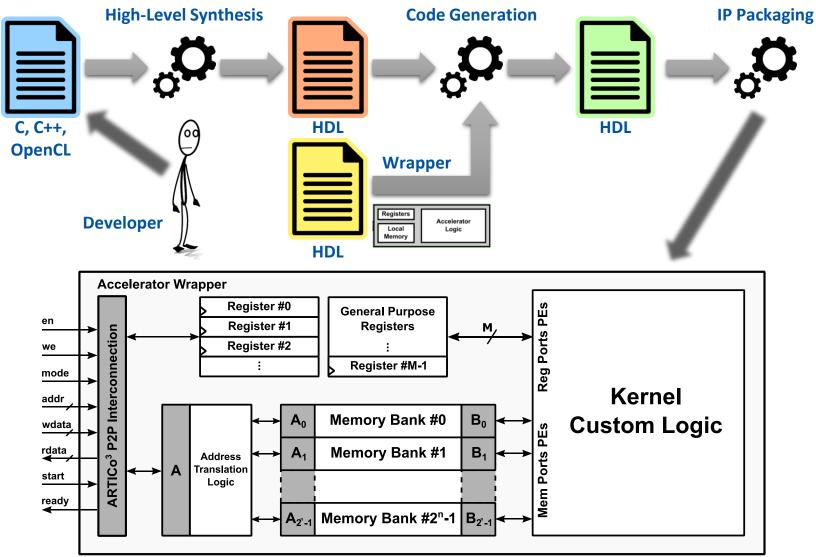

#### **Design Flows**

#### Runtime Environment

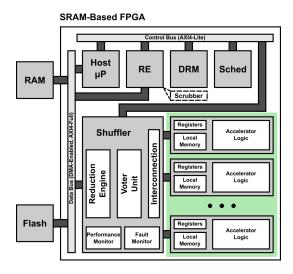

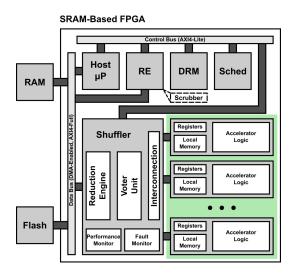

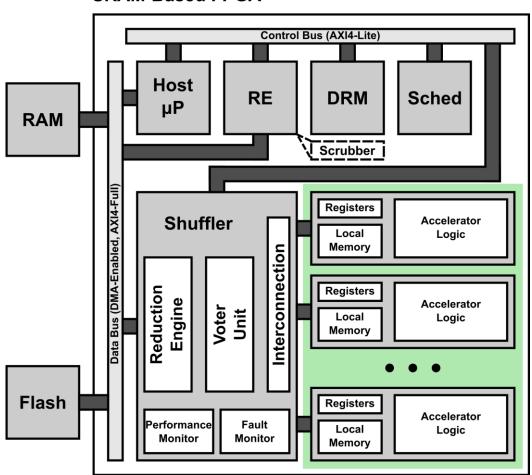

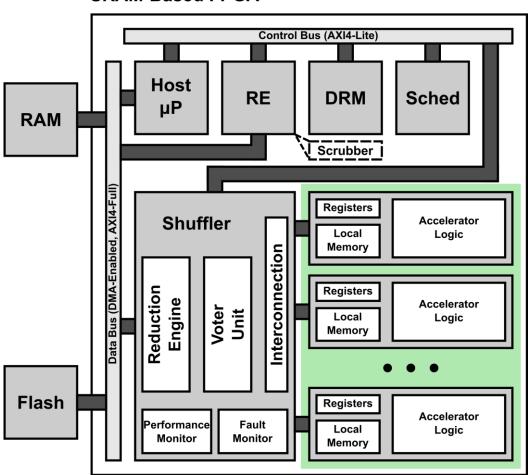

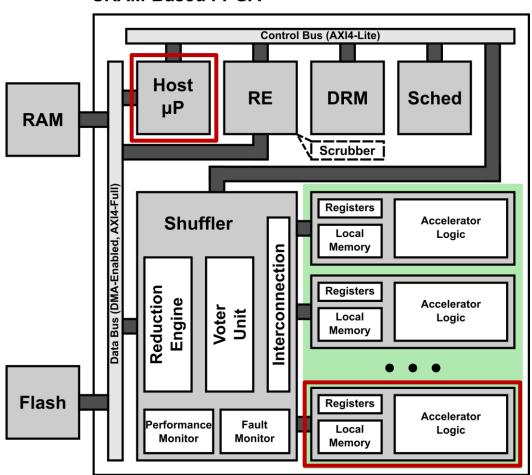

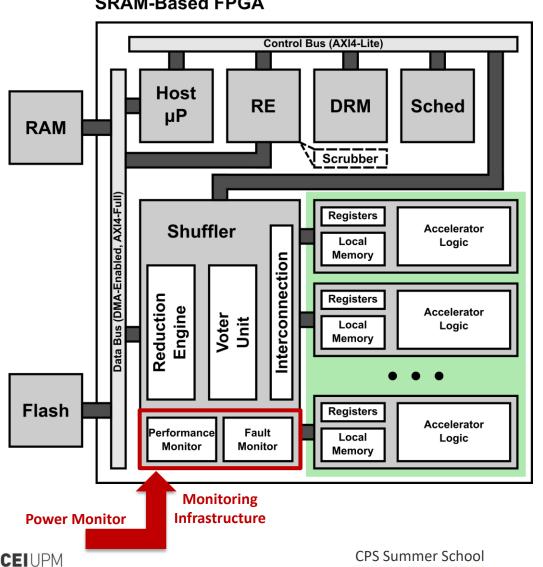

#### **SRAM-Based FPGA**

Arquitectura

Reconfigurable para el

Tratamiento

Inteligente de

Cómputo

Consumo

Confiabilidad

#### **SRAM-Based FPGA**

#### **SRAM-Based FPGA**

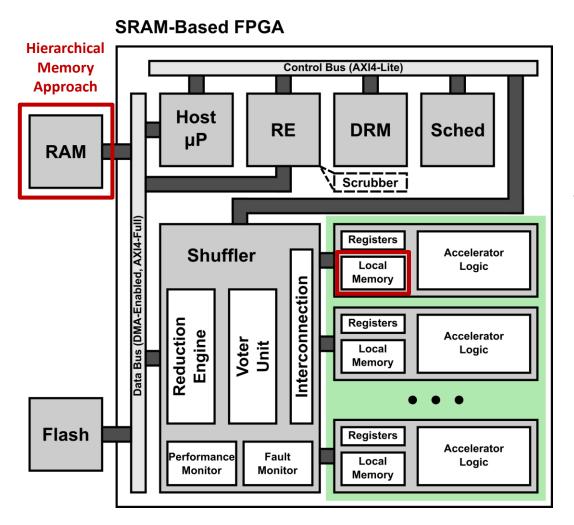

Reconfigurable

Architecture to enable

Smart

Management of

Performance

Energy Consumption

Dependability

Hardware Acceleration

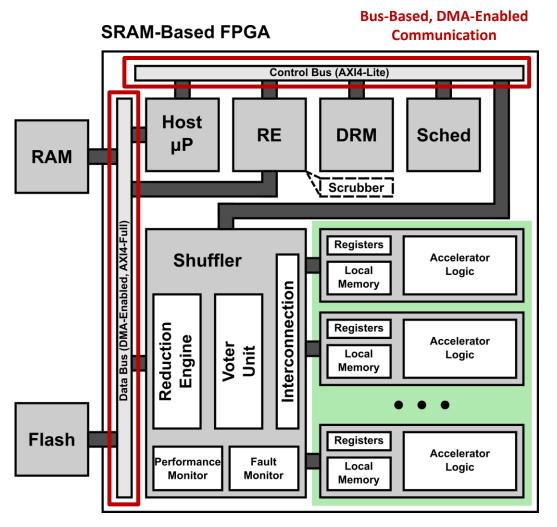

#### **SRAM-Based FPGA**

#### SRAM-Based FPGA

Reconfigurable Architecture to enable **S**mart Management of **P**erformance **E**nergy Consumption

**D**ependability

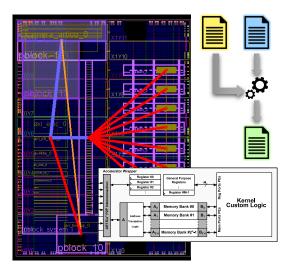

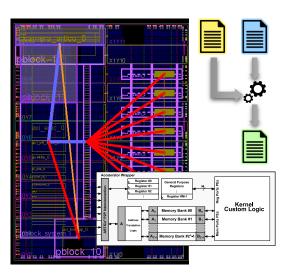

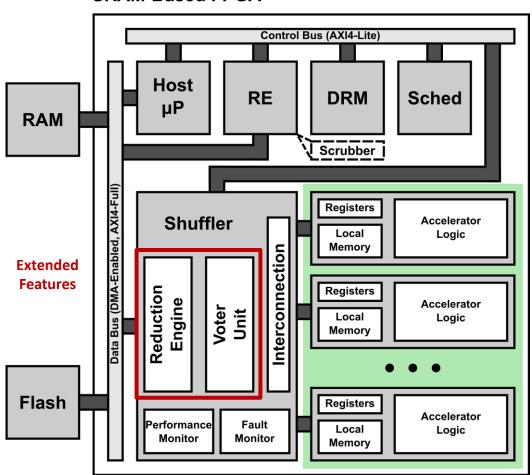

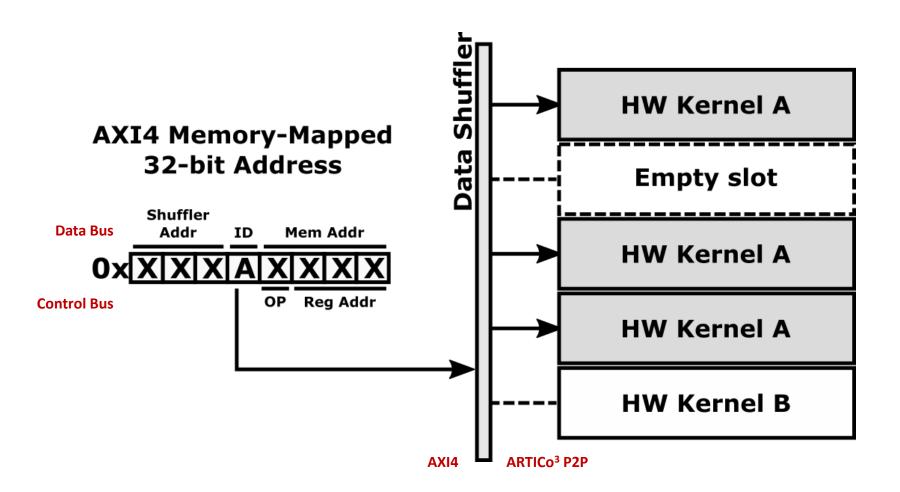

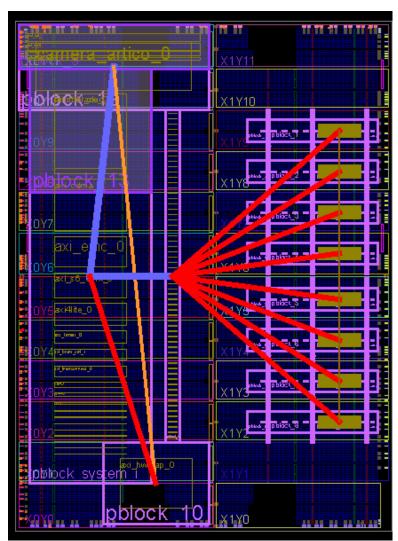

### **Accelerator Addressing**

#### **Low-Level Constraints**

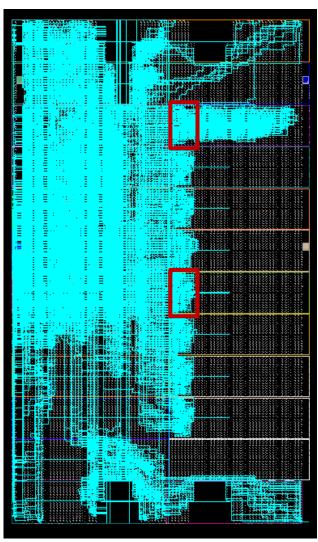

Design Placement

Design Placement

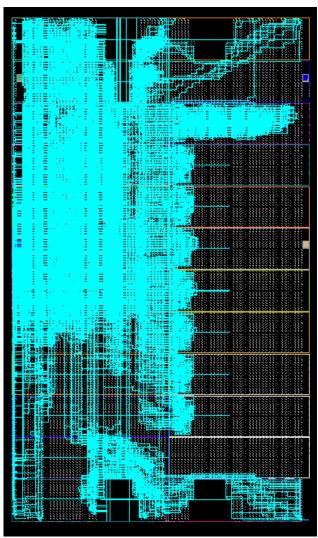

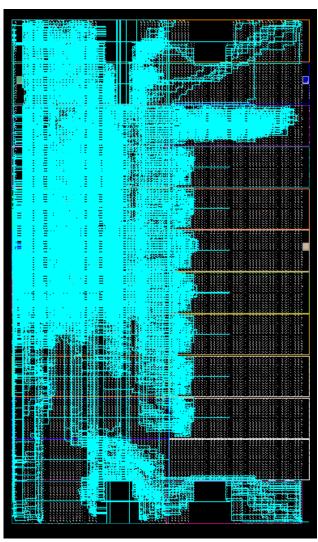

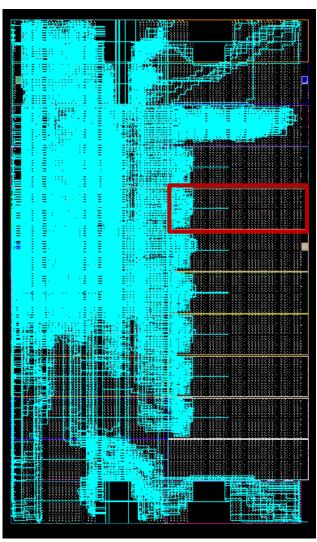

**Design Routing**

Design Placement

**Design Routing**

**Technology Dependencies**

#### **Low-Level Constraints**

Design Placement

**Design Routing**

#### **Technology Dependencies**

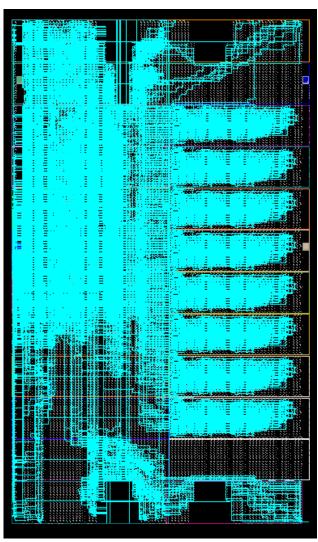

"Homogeneous" Fabric Layout

#### **Low-Level Constraints**

Design Placement

**Design Routing**

#### **Technology Dependencies**

"Homogeneous" Fabric Layout

Common Interfaces

#### **Low-Level Constraints**

Design Placement

**Design Routing**

#### **Technology Dependencies**

"Homogeneous" Fabric Layout

Common Interfaces

Hardware "Copy & Paste"

#### **Tutorial Outline**

- The ARTICo<sup>3</sup> repo

- What is included in the release available in the VM?

- Where are architecture, toolchain and runtime?

- I don't know how to set up an embedded Linux, can I use ARTICo<sup>3</sup>?

- Open Source (not available yet!): https://github.com/XXX/artico3.git

- Demo applications

- Dummy wait operation

- Parallel execution of different hardware kernels

- Debug mode (configuration and PMC registers dump)

- Matrix multiplication (yes, we know...)

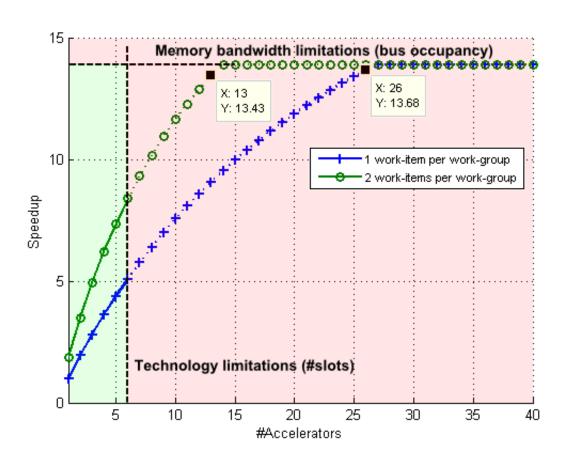

- Scalable execution performance

- Physical constraints and floorplanning

- How To...

- ...build an ARTICo<sup>3</sup> project from scratch?

- ...add new boards/devices?

#### **Tutorial** Fun time!

Universidad Politécnica de Madrid